## 1.0 INTRODUCTION

The WD37C65C Floppy Disk Subsystem Controller is an LSI device that provides all the needed functionality between the host processor and the floppy disk drive. This "superchip" integrates the following functions: formatter/controller, data separation, write precompensation, data rate selection (to a maximum of 1Mbit per second), and clock generation. It also provides interface drivers and receivers for the floppy drive.

The WD37C65C is functionally compatible pin-forpin with the WD37C65A/B. In addition the WD37C65C supports a power down mode for laptop and portable systems. Refer to Table 16-6 for a descripion of functional differences between the WD37C65A/B and the WD37C65C.

On the disk drive interface, the WD37C65C includes data separation designed to address high performance error rates on floppy disk drives. It contains all the necessary logic to achieve classical 2nd order, type 2, phase locked loop performance. Write precompensation is included, in addition to the usual formatting, encoding/decoding, stepper motor control, and status sensing functions. All inputs are TTL compatible Schmitt Trigger line receivers, and outputs are high current, open drain, with 48 mA drivers which meet the ANSI specification.

The host interface supports an 8 or 12 MHz, 286 microprocessor bus without the use of wait states. The inputs are Schmitt Triggers. Output drive capability is 20 LSTTL loads, allowing direct interconnection to bus structures without the use of buffers or transceivers. For PC, PC AT and EISA applications, qualification of interrupt request and DMA request is provided.

Traditionally, data rate selection, drive selection, and stepper motor control have been output ports of the host processor architecture. In the WD37C65C, these functions are latched into registers addressed within the I/O mapping of the system. The WD37C65C has eight internal registers. The eight bit main status register contains status information about the WD37C65C and may be accessed any time. Another four status registers under system control also give various status and error information. The Control

Register provides support logic that latches the two LSBs used to select the desired data rate that controls internal clock generation. The Operations Register replaces the standard latched port used in floppy subsystems. These registers are incorporated into the WD37C65C.

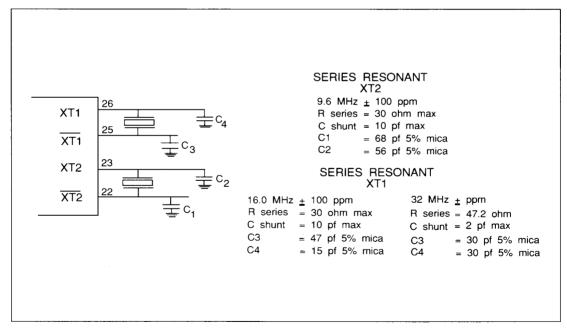

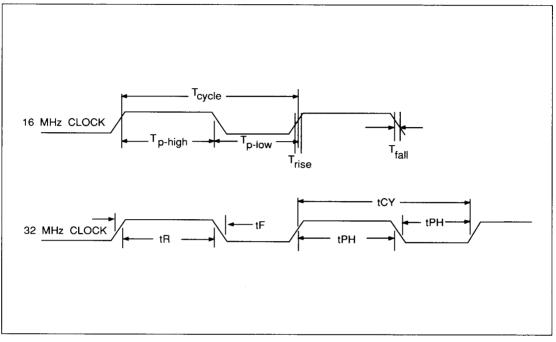

All Clock Generation: SCLK - Sampling Clock, WCLK-Write Clock, and MCLK - Master Clock, are included in the WD37C65C. XTAL oscillator circuits provide the necessary signals for internal timing when using the 44-pin PLCC. If the 40-pin DIP is used, the TTL level clock inputs must be provided. There are two oscillator inputs to the WD37C65C. The first at 32 MHz that handles all standard data rates (1 MB/s, 500, 250, and 125 kb/s or 16 MHz to handle 500, 250, and 125 kb/s). The second oscillator is at 9.6 MHz to support the 300 kb/sec data rate used in PC AT designs.

Some AT compatibles use two-speed disk drives. If a two-speed disk drive is used, the DRV input should be grounded along with the CLK2 input.

#### 1.1 FEATURES

- IBM PC AT compatible format (single and double density)

- —Provides "on chip" floppy control and operations

- —Provides required signal qualification to DMA channel when in PC AT mode

- —BIOS compatible

- —Supports dual speed spindle drives

- CMOS low power consumption (typically 300 mW at 32 MHz)

- Power down mode with low standby current (ICC = 100 μA maximum)

- Address mark detection circuitry (internal to floppy disk controller)

- Multi-sector and multi-track transfer capability

- Direct floppy disk drive interface (no buffers needed)

- -48 mA sink output drivers

- —Schmitt Trigger line receivers

Reprinted with permission of and licensed by NEC Electronics Inc. © 1985 NEC Electronics Inc.

//

- Compatible with PD8080/85, PD8086, 8088, 80286, 80386SX, 80386, and PD780 (Z80) microprocessors

- · On chip clock generation

- Two TTL clock inputs for 40-pin DIP

- Two XTAL oscillator circuits for 44-pin PLCC

- Automatic write precompensation

- -Disable option

- —Pin selectable inner track values of 125 or 187 nanoseconds

- Integrated high-performance DPLL data separator

- -Industry standard error rates of 10<E-9

- —Data rates of 125, 250, 300, 500 Kbits/second and 1Mbit/second

- —Option to select 150 Kbits/second FM and 300 Kbits/second MFM data rates only

- · Enhanced host interface

- -20 LSTTL output drive capability

- —TTL Schmitt trigger inputs

- User programmable track stepping rate and head load/unload times

- Supports four floppy or Micro Floppydisk drives with external decode logic

- Data transfer in DMA or non-DMA mode

- Parallel seek operation on a maximum of four drives

- Internal power up reset circuitry

- Single +5V DC power supply

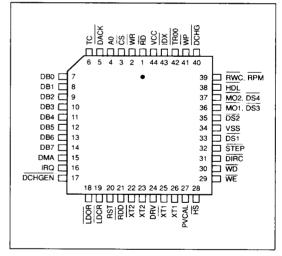

**40 PIN DIP**

**44 PIN PLCC**

# 2.0 SIGNAL DESCRIPTIONS

| D/P PIN<br>NUMBER | MNEMONIC        | SIGNAL NAME                   | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|-----------------|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 /1              | RD              | READ                          | I   | Control signal for transfer of data or status onto the data bus by the WD37C65C.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2/2               | WR              | WRITE                         | ŀ   | Control signal for latching data from the bus into the WD37C65C Buffer Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3/3               | <del>CS</del>   | CHIP SELECT                   | 1   | Selected when 0 (low) allowing $\overline{\rm RD}$ or $\overline{\rm WR}$ operation from the host.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4/4               | A0              | ADDRESS LINE                  | I   | Address line selecting data $(=1)$ or status $(=0)$ information. (A0 = logic 0 during WR is illegal except in Power Down mode.)                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5/5               | DACK            | DMA<br>ACKNOWLEDGE            | ı   | Used by the DMA controller to transfer data from the WD37C65C onto the bus. Logical equivalent to CS and A0=1. In Special or AT/EISA mode, this signal is qualified by DMAEN from the Operations Register.                                                                                                                                                                                                                                                                                                                                |

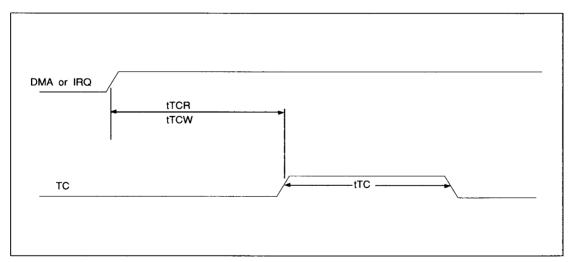

| 6/6               | TC              | TERMINAL-<br>COUNT            | l   | This signal indicates to WD37C65C that data transfer is complete. If DMA operational mode is selected for command execution, TC will be qualified by DACK, but not in the programmed I/O execution. In AT/EISA or Special mode, qualification by DACK requires the Operations Register signal DMAEN to be logically true. Note also that in AT/EISA mode, TC will be qualified by DACK, whether in DMA or non-DMA host operation. Programmed I/O in AT/EISA mode will cause an abnormal termination error at the completion of a command. |

| 7-14/<br>7-14     | DB0 thru<br>DB7 | DATA BUS 0 thru<br>DATA BUS 7 | I/O | 8-Bit, bi-directional, tristate, data bus. D0 is the least significant bit (LSB). D7 is the most significant bit (MSB).                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15/15             | DMA             | DIRECT<br>MEMORY<br>ACCESS    | 0   | DMA request for byte transfers of data. In Special of AT/EISA mode, this pin is tristated, enabled by the DMAEN signal from the Operations Register. This pin is driven in the Base mode.                                                                                                                                                                                                                                                                                                                                                 |

| 16/16             | IRQ             | INTERRUPT                     | 0   | Interrupt request indicating the completion of command execution or data transfer requests (in non-DMA mode). Normally driven in base mode. In Special or AT/EISA mode, this pin is tristated, enabled by the DMAEN signal from the Operations Register.                                                                                                                                                                                                                                                                                  |

**TABLE 2-1. SIGNAL DESCRIPTION**

//

11/18/91

<sup>\*</sup>Only in the PLCC version of the WD37C65C. Not connected in the DIP package.

| D/P PIN<br>NUMBER | MNEMONIC | SIGNAL NAME              | I/O | FUNCTION                                                                                                                                                                                         |

|-------------------|----------|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /17               | DCHGEN*  | DISK CHANGE<br>ENABLE    | I   | This input must be at Logic = 0 to enable DCHG input status at pin 40 to be placed on bit 7 of the data bus during a RD = 0 of LDCR = 0. It has Internal pull-up.                                |

| 17/18             | LDOR     | OPERATIONS<br>REGISTER   | I   | Address decode which enables the loading of the Operations Register. Internally gated with WR creates the strobe which latches the data bus into the Operations Register.                        |

| 18/19             | LDCR     | LOAD CONTROL<br>REGISTER | Ī   | Address decode which enables loading of the Control Register. Internally gated with $\overline{WR}$ creates the strobe which latches the two LSBs from the data bus into the Control Register.   |

| 19/20             | RST      | RESET                    | I   | Resets controller, placing microsequencer in idle.<br>Resets device outputs. Puts device in Base mode,<br>not PC AT or Special mode.                                                             |

| 20/21             | RDD      | READ DISK<br>DATA        | I   | This is the raw serial bit stream from the disk drive.<br>Each falling edge of the pulses represents a flux<br>transition of the encoded data.                                                   |

| 21/               | CLK2     | CLOCK2                   | I   | TTL level clock input used for non-standard data rates; is 9.6 MHz for 300 kb/s, and can only be selected from the Control Register.                                                             |

| /22               | XT2      | XTAL2                    | 0   | XTAL oscillator drive output for 44-pin PLCC (See Figure 6). Should be left floating if TTL inputs used at pin 23.                                                                               |

| /23               | XT2      | XTAL2                    | I   | XTAL oscillator input used for non-standard data rates. It may be driven with a TTL level signal.                                                                                                |

| 22/24             | DRV      | DRIVE TYPE               | I   | Drive type input indicates to the device that a twospeed spindle motor is used if logic is 0. In that case, the second clock input will never be selected and must be grounded.                  |

| 23/               | CLK1     | CLOCK1                   | I   | TTL level clock input is used to generate all internal timings for standard data rates. Frequency must be $16 MHz \pm 0.1\%$ or $32 MHz \pm 0.1\%$ , and may have $40/60$ or $60/40$ duty cycle. |

| /25               | XT1      | XTAL1                    | 0   | XTAL oscillator drive output for 44-pin PLCC (See Figure 6). Should be left floating if TTL inputs are used at pin 26.                                                                           |

| /26               | XT1      | XTAL1                    | I   | XTAL oscillator input requiring 16 MHz or 32 MHz crystal. This oscillator is used for all standard data rates, and may be driven with a TTL level signal.                                        |

**TABLE 2-1. SIGNAL DESCRIPTION (CONTINUED)**

//

<sup>\*</sup>Only in the PLCC version of the WD37C65C. Not connected in the DIP package.

26-5

| D/P PIN<br>NUMBER | MNEMONIC | SIGNAL NAME                   | I/O | FUNCTION                                                                                                                                                                                                                                                                                   |

|-------------------|----------|-------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24/27             | PCVAL    | PRECOMPEN-<br>SATIONVALUE     | ı   | Precompensation value select input. This pin determines the amount of write precompensation used on the inner tracks of the diskette. Logic 1 = 125 ns, Logic 0 = 187 ns. If the defeat option is used, PCVAL is unimportant and precompensation is disabled.                              |

| 25/28             | HS       | HEAD SELECT                   | 0   | High current driver (HCD) output selects the head (side) of the floppy disk that is being read or written.<br>Logic 1 = side 0. Logic 0 = side 1.                                                                                                                                          |

| 26/29             | WE       | WRITE ENABLE                  | 0   | This HCD output becomes true, active low, just prior to writing on the diskette. This allows current to flow through the write head.                                                                                                                                                       |

| 27/30             | WD       | WRITE DATA                    | 0   | This HCD output is WRITE DATA. Each falling edge of the encoded data pulse stream causes a flux transition on the media.                                                                                                                                                                   |

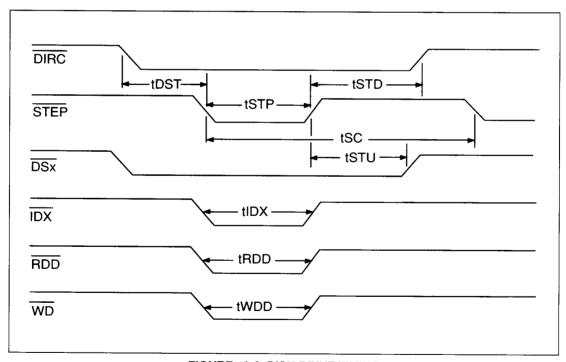

| 28/31             | DIRC     | DIRECTION                     | 0   | This HCD output determines the direction of the head stepper motor. Logic 1 = outward motion. Logic 0 = inward motion.                                                                                                                                                                     |

| 29/32             | STEP     | STEP PULSE                    | 0   | This HCD output issues an active low pulse for each track to track movement of the head.                                                                                                                                                                                                   |

| 30/33             | DS1      | DRIVE SELECT 1                | 0   | This HCD output, when active low, is DRIVE SELECT 1 in AT/EISA mode. It enables the interface to this disk drive. This signal comes from the Operations Register. In Base, or Special mode, this output is #1 of the four decoded Unit Selects, as specified in the device command syntax. |

| 31/34             | VSS      | GROUND                        |     | Ground.                                                                                                                                                                                                                                                                                    |

| 32/35             | DS2      | DRIVE SELECT 2                | 0   | This HCD output, when active low, is DRIVE SELECT 2 in AT/EISA mode, enables the interface to this disk drive. This signal comes from the Operations Register. In Base or the Special mode, this output is #2 of the four decoded Unit Selects as specified in the device command syntax.  |

| 33/36             | MO1, DS3 | MOTOR ON 1,<br>DRIVE SELECT 3 | 0   | This HCD output, when active low, is MOTOR ON enable for disk drive #1, in AT/EISA mode. This signal comes from the Operations Register. In the Base or Special mode, this output is #3 of the four decoded Unit Selects as specified in the device command syntax.                        |

**TABLE 2-1. SIGNAL DESCRIPTION (CONTINUED)**

11/18/91

**//**/

<sup>\*</sup>Only in the PLCC version of the WD37C65C. Not connected in the DIP package.

| D/P PIN<br>NUMBER | MNEMONIC | SIGNAL NAME                                               | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------|-----------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34/37             | MO2, DS4 | MOTOR ON 2,<br>DRIVE SELECT 4                             | 0   | This HCD output, when active low, is MOTOR ON enable for disk drive #2, in AT/EISA mode. This signal comes from the Operations Register. In the Base or Special mode, this output is #4 of the four decoded Unit Selects as specified in the device command syntax.                                                                                |

| 35/38             | HDL      | HEAD LOADED                                               | 0   | This HCD output, when active low, causes the head to be loaded against the media in the selected drive.                                                                                                                                                                                                                                            |

| 36/39             | RWC, RPM | REDUCED<br>WRITE<br>CURRENT,<br>REVOLUTIONS<br>PER MINUTE | 0   | This HCD output, when active low, causes a REDUCED WRITE CURRENT, when bit density is increased toward the inner tracks, becoming active when tracks >28 are accessed. This condition is valid for Base or Special mode, and is indicative of when write precompensation is necessary. In the AT/EISA mode, this signal will be active when CR0=1. |

| /40               | DCHG*    | DISK CHANGE                                               | I   | This Schmitt Trigger (ST) input senses status from the drive. Active low indicates that drive door is open or that the diskette has possibly changed since the last drive selection. It has internal pull-up.                                                                                                                                      |

| 37/41             | WP       | WRITE<br>PROTECTED                                        | 1   | This ST input senses status from the disk drive indicating active low when a diskette is WRITE PROTECTED.                                                                                                                                                                                                                                          |

| 38/42             | TR00     | TRACK 00                                                  | 1   | This ST input senses status from disk drive, indicating active low when the head is positioned over the outermost track, TRACK 00.                                                                                                                                                                                                                 |

| 39/43             | ĪDX      | INDEX                                                     | ı   | This ST input senses status from the disk drive, indicating active low when the head is positioned over the beginning of a track marked by an index hole.                                                                                                                                                                                          |

| 40/44             | VCC      | +5VDC                                                     |     | Input power supply.                                                                                                                                                                                                                                                                                                                                |

|                   |          |                                                           |     |                                                                                                                                                                                                                                                                                                                                                    |

**TABLE 2-1. SIGNAL DESCRIPTION (CONTINUED)**

//

<sup>\*</sup>Only in the PLCC version of the WD37C65C. Not connected in the DIP package.

26-7

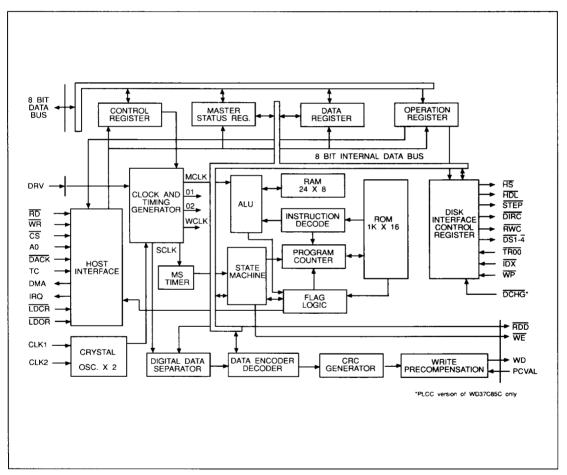

# 3.0 ARCHITECTURE

The WD37C65C Floppy Disk Subsystem Controller is an LSI device that provides all the needed functionality between the host processor and the floppy disk drive. This "superchip" integrates: formatter/controller, data separation, write precompensation, data rate selection, clock generation, drive interface drivers and receivers.

Figure 3-1 illustrates a block diagram of the WD37C65C Floppy Disk Subsystem Controller.

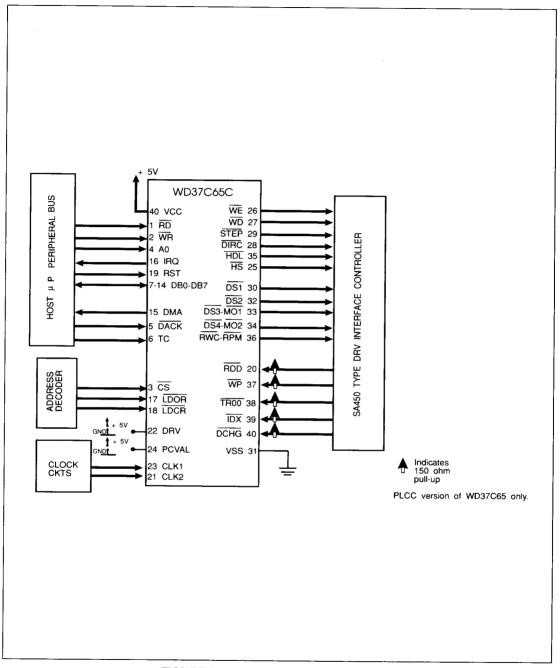

Figure 3-2 illustrates a typical WD37C65C system

FIGURE 3-1. WD37C65C BLOCK DIAGRAM

11/18/91

**//**//

FIGURE 3-2. TYPICAL WD37C65 SYSTEM

# 4.0 HOST INTERFACE

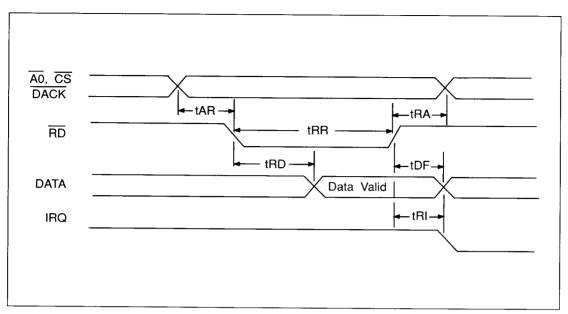

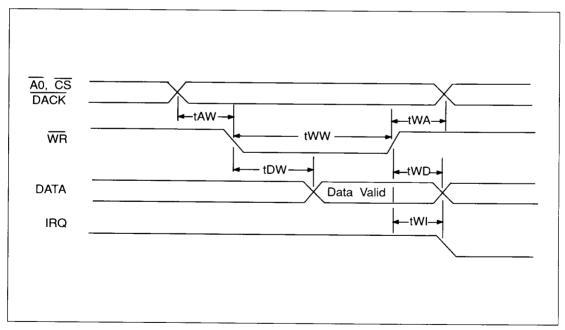

The host interface is the Host Microprocessor Peripheral Bus. This bus is composed of eight control signals and eight data signals. In the Special or AT/EISA modes, IRQ and DMA request are tri-stated and qualified by DMA enable which is provided by the Operations Register. The data bus, DMA, and IRQ outputs are designed to handle 20 LSTTL loading. Inputs are Schmitt Trigger receivers and can be hooked up to a bus or backplane without any additional buffering.

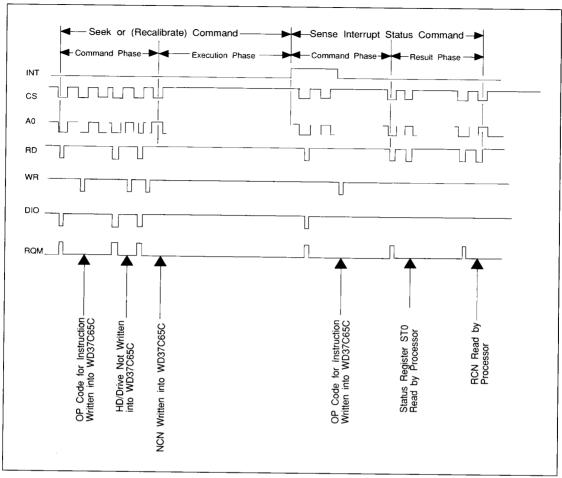

During the Command or Result phases, the Main Status Register must be read by the processor before each byte of information is written into or read from the Data Register. After each byte of data is read from or written into the Data Register, the CPU waits for 12 us before reading the Main Status Register, Bits D6 and D7 in the Main Status Register must be in a 0 and 1 state, respectively, before each byte of the command word may be written into the WD37C65C. Many of the commands require multiple bytes. As a result, the Main Status Register must be read prior to each byte transfer to the WD37C65C. During the Result phase. Bits D6 and D7 in the Main Status Register must both be 1's (D6=1 and D7=1) before reading each byte from the Data Register. Note that this reading of the Main Status Register before each byte transfer to the WD37C65C is required only in the Command and Result phases, and not during the Execution phase. Note also that DB6 and DB7 in the MSR can be polled instead of waiting 12 µs.

During the Execution phase, the Main Status Register need not be read. If the WD37C65C is in the non-DMA Mode, then the receipt of each data byte (WD37C65C is reading data from the FDD) is indicated by an interrupt signal on pin 16 (IRQ=1). The generation of a Read signal (RD = 0) clears the interrupt and sends the data onto the data bus. If the processor cannot handle interrupts fast enough (every 13  $\mu$ s for the MFM mode and 27  $\mu$ s for the FM mode), then it may poll the Main Status Register and bit D7 (RQM) functions as the Interrupt signal. If a Write Command is in process then the WR signal performs the reset to the Interrupt signal.

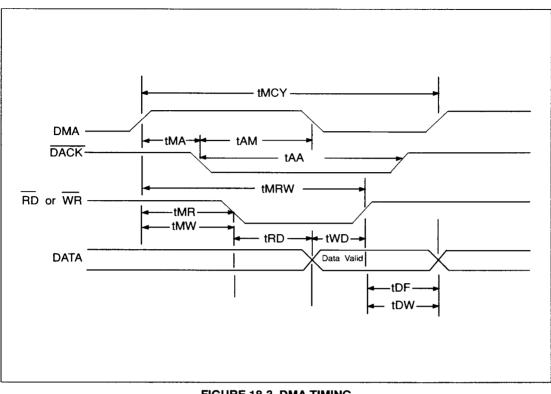

All timings mentioned above double for mini floppy data rates. Note that in the non-DMA mode it is necessary to examine the Main Status Register to determine the cause of the interrupt since it could be a data interrupt or a command termination interrupt. either normal or abnormal. If the WD37C65C is in the DMA mode, no interrupt signals are generated during the Execution phase. The WD37C65C generates DMA's (DMA Requests) when each byte of data is available. The DMA Controller responds to this request with both DACK=0 (DMA Acknowledge) and an RD=0 (Read signal). When the DMA Acknowledge signal goes low (DACK=0), the DMA Request is cleared (DMA=0) If a Write Command has been issued, then a WR signal will appear instead of RD. After the Execution phase has been completed (Terminal Count has occurred) or the EOT sector read/written. then an Interrupt will occur (IRQ = 1). This signifies the beginning of the Result phase. When the first byte of data is read during the Result phase, the interrupt is automatically cleared (IRQ = 0).

Note that in PC AT usage, non-DMA Host transfers are not the normal procedure. If the user chooses to do so, the WD37C65C will successfully complete commands, but will always give abnormal termination error status since TC is qualified by an inactive DACK.

The RD or WR signals should be asserted while DACK is true. The CS signal is used in conjunction with RD and WR as a gating function during programmed I/O operations. CS has no effect during DMA operations. If the non-DMA mode is chosen, the DACK signal should be pulled up to Vcc. Note that during the Result phase all bytes shown in the Command Table must be read. The Read Data Command, for example, has several bytes of data in the Result phase. All seven bytes must be read in order to successfully complete the Read Data command. The WD37C65C will not accept a new command until all seven bytes have been read. Other commands may require fewer bytes to be read during the Result phase. The WD37C65C contains five Status Registers. The Main Status Register mentioned may be read by the processor at any time. The other four Status Registers (ST0, ST1, ST2, and ST3) are available only during the Result phase and may be read only after completing a command. The particular command that has been executed

1/2

determines how many of the Status Registers will be read.

The bytes of data which are sent to the WD37C65C to form the Command phase, and are read out of the WD37C65C in the Result phase, must occur in the order shown in the Command Table. The command code must be sent first and the other bytes sent in the prescribed sequence.

No foreshortening of the Command or Result phases is allowed. After the last byte of data in the Command phase is sent to the WD37C65C, the Execution phase automatically starts. In a similar fashion, when the last byte of data is read out in the Result phase, the command is automatically ended and the WD37C65C is ready for a new command.

## 5.0 CONTROL REGISTER

The Control Register is a write only register that is used to set the data transfer rate and disable write precompensation. It provides support logic that latches the two LSBs of the data bus upon receiving LDCR and WR. CS should not be active when this happens. These bits are used to select the desired data rate, which in turn controls the internal clock generation. Clock switchover is internally "deglitched," allowing continuous operation after changing data rates. If the Control Register is not used, the data rate is governed by the supplied clock or crystal. The frequency must be 64 times the desired MFM data rate. This implies a maximum data rate of 250 kb/s for a frequency of 16 MHz or a maximum data rate of 500 Kb/s for a frequency of 32 MHz, unless the Control Register is used. Switching of this clock must be "glitchless" or the device will need to be reset. Table 5-1 and Table 5-2 present the Control Register configuration for 16 MHz and 32 MHz frequencies, respectively.

The WD37C65C optionally supports 150 kb/s FM data transfer rate. The Control Register configuration is shown in Table 5-3. The 150 kb/s data rate can be selected by using a 9.6 MHz XTAL or TTL level clock input on pin 26 (44-pin PLCC) or pin 23 (40-pin DIP). Only two data transfer rates can be selected with this configuration: 150 kb/s FM and 300 kb/s MFM.

| CR1 | CR0 | DRV | DATA RATE | COMMENTS           | RPM<br>(AT/EISA MODE) |

|-----|-----|-----|-----------|--------------------|-----------------------|

| 0   | 0   | x   | 500 K     | MFM                | 1                     |

| 0   | 0   | x   | 250 K     | FM                 | 1                     |

| 0   | 1   | 0   | 250 K     | MFM                | 0                     |

| 0   | 1   | 1   | 300 K     | MFM,(9.6 MHz XTAL) | 0                     |

| 1   | 0   | x   | 250 K     | MFM, RST Default   | 1                     |

| 1   | 0   | x   | 125 K     | FM, RST Default    | 1                     |

TABLE 5-1, CONTROL REGISTER CONFIGURATION - 16 MHZ

| CR1 | CR0 | DRV | DATA RATE | COMMENTS           | RPM<br>(AT/EISAMODE) |

|-----|-----|-----|-----------|--------------------|----------------------|

| 0   | 0   | x   | 1 M       | MFM                | 1                    |

| 0   | 0   | х   | 500 K     | FM                 | 1                    |

| 0   | 1   | 0   | 500 K     | MFM                | 0                    |

| 0   | 1   | 1   | 300 K     | MFM,(9.6 MHz XTAL) | 0                    |

| 1   | 0   | ×   | 500 K     | MFM, RST Default   | 1                    |

**TABLE 5-2. CONTROL REGISTER CONFIGURATION - 32 MHz**

**//**/

In AT/EISA mode, write precompensation can be disabled by a logic high on bit 2 of the Control Register. (See Table 5-4).

| CR1 | CR0 | DRV | DATA RATE | COMMENTS | RPM<br>(AT/EISA MODE) |

|-----|-----|-----|-----------|----------|-----------------------|

| 0   | 0   | x   | 300 K     | MFM      | 1                     |

| 0   | 0   | х   | 150 K     | FM       | 1                     |

**TABLE 5-3. CONTROL REGISTER CONFIGURATION - OPTIONS**

| Bit | SIGNAL NAME AND FUNCTION | RESET CONDITION | CLOCK QUALIFIER |

|-----|--------------------------|-----------------|-----------------|

| 0   | Data Rate                | 0               | None            |

| 1   | Data Rate                | 0               | None            |

| 2   | No Write Precompensation | 0               | None            |

| 3-7 | Reserved                 | None            | None            |

TABLE 5-4. CONTROL REGISTER CONFIGURATION - AT/EISA MODE

## 6.0 MASTER STATUS REGISTER

The Master Status Register is an eight-bit, read/write register that contains the status information of the FDC. It can be accessed at any time. The WD35C65C provides a write only register, called Master Status Register 1 (MSR1) which is used only to select power down mode. In power down mode the XTAL oscillator, controller circuitry and all linear circuitry are turned off so that the controller draws very low current. Normal operation is restored by asserting reset to the WD37C65C. See Master Status Register 1.

Only the Master Status Register may be read and used to facilitate the transfer of data between the processor and WD37C65C. The DIO and RQM bits in the Master Status Register indicate when data is ready and in which direction data will be transferred on the data bus. The maximum time between the last RD or WR during a Command or Result phase and the setting of DIO and RQM is 12 µs if 500 kb/s MFM data rate is selected. (If 250 kb/s MFM is selected, the delay is 24 us. If 1 Mb/s is selected, the delay is 6 µs.) For this reason, everytime the Master Status Register is read, the CPU should wait 12 µs. The maximum time from the trailing edge of the last RD in the result phase to when DB4 (FDC busy) goes low is 12 us.

The bits in the Master Status Register are listed in Table 6-1. The bits in Status Register 0 are listed

in Table 6-2. The bits in Status Register 1 are listed in Table 6-3. The bits in Status Register 2 are listed in Table 6-4. The bits in Status Register 3 are listed in Table 6-5.

# 6.1 MASTER STATUS REGISTER 1 (MSR1--WRITE ONLY)

The WD37C65C will enter power down mode, when bit 0 of MSR1 is set to logical "1" and the following conditions are met:

- 1. The RST pin to the FDC is inactive.

- 2. Bit 2 in the Operations Register is "SRST/= 1".

- 3. The WD37C65C is awaiting a command from the host.

The WD37C65C can also be programmed with external logic to automatically enter power down mode a few milliseconds after the beginning of idle mode.

Normal operation is restored when the RST pin to the FDC is active and the FDC is reset. This in turn resets bit 0 of MSR1 register to logic 0. The bits in the Master Status Register are listed in Table 6-2.

| BIT | SIGNAL NAME & FUNCTION | RESET CONDITION | CLOCK QUALIFIER |

|-----|------------------------|-----------------|-----------------|

| 0   | Power down mode (PDM)  | 0               | None            |

| 1-7 | Reserved               | None            | None            |

TABLE 6-1, AT/EISA MODE, MASTER STATUS REGISTER 1 CONFIG.

|     | BIT                   |        |                                                                                                                                                                                                          |

|-----|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                  | SYMBOL | DESCRIPTION                                                                                                                                                                                              |

| DB0 | FDD 0 BUSY            | DOB    | FDD number is 0 in the Seek Mode. If any of the bits is set, FDC will not accept READ or WRITE commands.                                                                                                 |

| DB1 | FDD 1 BUSY            | D1B    | FDD number 1 is in the Seek Mode. If any of the bits is set, FDC will not accept READ or WRITE commands.                                                                                                 |

| DB2 | FDD 2 BUSY            | D2B    | FDD number 2 is in the Seek Mode. If any of the bits is set, FDC will not accept READ or WRITE commands.                                                                                                 |

| DB3 | FDD 3 BUSY            | D3B    | FDD number 3 is in the Seek Mode. If any of the bits is set, FDC will not accept READ or WRITE commands.                                                                                                 |

| DB4 | FDC BUSY              | СВ     | A READ or WRITE command is in progress. FDC will not accept any other command.                                                                                                                           |

| DB5 | EXECUTION<br>MODE     | EXM    | This bit is set only during Execution phase in non-<br>DMA mode. When DB5 goes low Execution phase<br>has ended and Results Phase has started. It<br>operates only during non-DMA mode of operation.     |

| DB6 | DATA INPUT            | DIO    | Indicates direction of data transfer between FDC and Data Register. If DIO=1, then transfer is from Data Register to the processor. If DIO=0, then transfer is from the processor to Data Register.      |

| DB7 | REQUEST FOR<br>MASTER | RQM    | Indicates Data Register is ready to send or receive data to or from the processor. Both bits DIO and RQM should be used to perform the handshaking functions of "ready" and "direction" to the processor |

TABLE 6-2. STATUS REGISTER 0 BITS

|     | BIT                |        |                                                                                                                                                                                                              |

|-----|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME               | SYMBOL | DESCRIPTION                                                                                                                                                                                                  |

| D7  | INTERRUPT<br>CODE  | IC     | D7=0 and D6=0. Normal termination of command was completed and properly executed. D7=0 and D6=1. Abnormal termination of command, (AT). Execution of command was started but was not successfully completed. |

| D6  |                    |        | D7=1 and D6=0. Invalid command issue, (IC). Command which was issued was never started.                                                                                                                      |

| D5  | SEEK END           | SE     | When the FDC completes the SEEK command, this flag is set to 1 (high).                                                                                                                                       |

| †D4 | EQUIPMENT<br>CHECK | EC     | If the Track 0 signal fails to occur after 77 step pulses per Recalibrate Command, then this flag is set.                                                                                                    |

| †D3 | NOT READY          | NR     | Since drive Ready is always presumed true, this will always be a logic 0.                                                                                                                                    |

| D2  | HEAD SELECT        | HS     | This flag is used to indicate the state of the head at interrupt.                                                                                                                                            |

| D1  | UNIT SELECT 1      | US1    | This flag is used to indicate a Drive Unit Number at interrupt.                                                                                                                                              |

| D0  | UNIT SELECT 0      | US0    | This flag is used to indicate a Drive Unit Number at interrupt.                                                                                                                                              |

**TABLE 6-3. STATUS REGISTER 1 BITS**

|     | BIT                     |        |                                                                                                                                                                                                   |

|-----|-------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                    | SYMBOL | DESCRIPTION                                                                                                                                                                                       |

| D7  | END OF<br>CYLINDER      | EN     | When the FDC tries to access a sector beyond the final sector of a cylinder, this flag is set.                                                                                                    |

| D6  |                         |        | Not used. This bit is always 0 (low).                                                                                                                                                             |

| D5  | DATA ERROR              | DE     | When the FDC detects a *CRC error in either the ID field or the data field, this flag is set.                                                                                                     |

| D4  | OVERRUN                 | OR     | If the FDC is not serviced by the host system during data transfers within a certain time interval, this flag is set.                                                                             |

| DЗ  |                         |        | Not used. This bit is always 0 (low).                                                                                                                                                             |

| D2  | NO DATA                 | ND     | During execution of READ DATA, WRITE DELETED DATA, or SCAN command, if the FDC cannot find the sector specified in the **IDR Register, this flag is set.                                          |

|     |                         |        | During execution of the READ ID command, if the FDC cannot read the ID field without an error, then this flag is set.                                                                             |

|     |                         |        | During execution of the READ A TRACK command, if the starting sector cannot be found, then this flag is set.                                                                                      |

| D1  | NOT WRITEABLE           | NW     | During execution of WRITE DATA, WRITE DELETED DATA or FORMAT A TRACK commands, if the FDC detects a WP signal from the FDD, then this flag is set.                                                |

| D0  | MISSING<br>ADDRESS MARK | MA     | If the FDC cannot detect the ID Address Mark after encountering the index hole twice, then this flag is set.                                                                                      |

|     |                         |        | If the FDC cannot detect the Data Address Mark or<br>Deleted Data Address Mark, this flag is set. At the<br>same time the MD (Missing Address Mark in data<br>field) of Status Register 2 is set. |

**TABLE 6-4. STATUS REGISTER 2 BITS**

|     | BIT                                      |        |                                                                                                                                                                          |

|-----|------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                                     | SYMBOL | DESCRIPTION                                                                                                                                                              |

| D7  |                                          |        | Not Used. This bit is always 0 (low).                                                                                                                                    |

| D6  | CONTROL MARK                             | СМ     | During execution of the READ DATA or SCAN Command, if the FDC encounters a sector which contains a Deleted Data Address Mark, this flag is set.                          |

| D5  | DATA ERROR                               | DD     | If the FDC detects a CRC error in the data field, then this flag is set.                                                                                                 |

| D4  | WRONG<br>CYLINDER                        | wc     | This bit is related to the ND bit, and when the contents of * * *C on the medium is different from that stored in the IDR, this flag is set.                             |

| D3  | SCAN EQUAL                               | SH     | During execution of the SCAN command, if the condition of "equal" is satisfied, this flag is set.                                                                        |

| D2  | SCAN NOT                                 | SN     | During execution of the SCAN command, if the FDC cannot find a sector on the cylinder which meets the condition, then this flag is set.                                  |

| D1  | BAD CYLINDER                             | BC     | This bit is related to the ND bit, and when the contents of C on the medium is different from that stored in the IDR and the contents of C is FF, then this flag is set. |

| D0  | MISSING<br>ADDRESS MARK<br>IN DATA FIELD | MD     | When data is read from the medium, if the FDC cannot find a Data Address Mark or Deleted Data Address Mark, then this flag is set.                                       |

**TABLE 6-5. STATUS REGISTER 3 BITS**

|     | BIT                |        |                                                                                                     |

|-----|--------------------|--------|-----------------------------------------------------------------------------------------------------|

| NO. | NAME               | SYMBOL | DESCRIPTION                                                                                         |

| †D7 |                    |        | Not used. Will always be logic 0.                                                                   |

| D6  | WRITE<br>PROTECTED | WP     | This bit is used to indicate the status of the WRITE PROTECTED signal from the FDD.                 |

| †D5 | READY              | RY     | This bit will always be a logic 1. Drive is presumed to be ready.                                   |

| D4  | TRACK 0            | ТО     | This bit is used to indicate the status of the Track 0 signal from the FDD.                         |

| †D3 | WRITE<br>PROTECTED | WP     | This bit is used by the WD37C65C to indicate the status of the WRITE PROTECTED signal from the FDD. |

| D2  | HEAD SELECT        | HS     | This bit is used to indicate the status of the Side Select signal to the FDD.                       |

| D1  | UNIT SELECT 1      | US1    | This bit is used to indicate the status of the Unit Select 1 signal to the FDD.                     |

| D0  | UNIT SELECT 2      | US0    | This bit is used to indicate the status of the Unit Select 0 signal to the FDD.                     |

# **TABLE 6-6. MASTER STATUS REGISTER BITS**

\* CRC - Cyclic Redundancy Check

\* \* \* C - Cylinder

\* \* IDR - Internal Data Register

† - Different from NEC765

# 7.0 DATA REGISTER

The eight-bit Data Register stores data, commands, parameters, and FDD status information. Data bytes are read out of, or written into, the Data Register in order to program or obtain the results after a particular command.

The relationship between the Master Status Register and the Data Register and the signals RD, WR, and A0 are shown in Table 7-1.

| A0 | RD | WR | FUNCTION                  |  |

|----|----|----|---------------------------|--|

| 0  | 0  | 1  | Read Main Status Register |  |

| 0  | 1  | 0  | Illegal                   |  |

| 0  | 0  | 0  | Illegal                   |  |

| 1  | 0  | 0  | Illegal                   |  |

| 1  | 0  | 1  | Read from Data Register   |  |

| 1  | 1  | 0  | Write into Data Register  |  |

TABLE 7-1. MASTER STATUS AND DATA REGISTERS RELATIONSHIPS

# 8.0 OPERATIONS REGISTER

The Operations Register provides support logic that latches the data bus upon receiving LDOR and WR. CS should not be active when this happens. The Operations Register replaces the typical latched port found in floppy subsystems used

to control disk drive spindle motors and to select the desired disk drive. Table 8-1 represents the Operations Register.

| NO. | SYMBOL | DESCRIPTION                                                                                                                      |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| OR0 | DSEL   | Drive Select, if low and MOEN1 = 1, then DS1 is active. If high and MOEN2 = 1, then DS2 is active, but only in the AT/EISA mode. |

| OR1 | (x)    | This must be a logic O for DS1 and DS2 to become active.                                                                         |

| OR2 | SRST   | Soft reset, active low.                                                                                                          |

| OR3 | DMAEN  | DMA enable, active in Special and AT/EISA modes. Qualifies DMA and IRQ outputs and DACK input.                                   |

| OR4 | MOEN1  | Motor On enable, inverted output M01 is active only in AT/EISA mode.                                                             |

| OR5 | MOEN2  | Motor On enable, inverted output M02 is active only in AT/EISA mode.                                                             |

| OR6 | (X )   | Has no defined function. A spare.                                                                                                |

| OR7 | (MSEL) | Mode Select. During a soft reset condition, may be used to select between Special mode (1) and AT/EISA mode (0).                 |

**TABLE 8-1. OPERATIONS REGISTER**

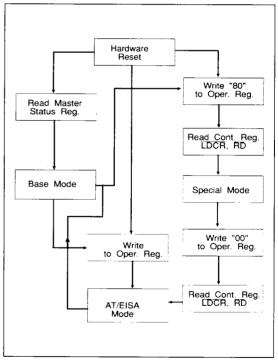

# 9.0 BASE, SPECIAL, AND AT/EISA MODES

Base, Special, PC AT and EISA modes allow subtle differences which the user may find desirable. The Control Register may be used in any mode without altering functionality.

#### 9.1 BASE MODE

After a hardware reset, RST active, the WD37C65C will be held in soft reset, SRST active, with the normally driven signals, DMA request and IRQ request outputs tristated. Base mode may be initiated at this time by a chip access by the host. Although this may be any read or write, it is strongly recommended that the Base mode user's first chip access be a read of the Master Status Register. Once Base mode is entered, the soft reset is released, and IRO and DMA are driven. Base mode prohibits the use of the Operations Register, hence there can be no qualifying by DMAEN and no soft resets. The Drive Select outputs, DS1 to DS4, offer a 1 of 4 decoding of the Unit Select bits resident in the command structure. Pin RWC represents Reduce Write Current and is indicative of when write precompensation is necessary.

#### 9.2 SPECIAL MODE

Special mode allows use of the Operations Register for the DMAEN signal as a qualifier and to do a software driven device reset, SRST. To enter Special mode, the Operations Register is loaded with (1 X 0 0 X 0 X X), setting mode Select to a logic 1 disabling MOEN1 and MOEN2 and causing SRST to be active. Then a read of the Control Register address, LDCR and RD, places the device in Special mode. The DS1 through DS4 is again offered in this mode, as is RWC.

#### 9.3 AT/EISA MODES

For AT/EISA compatibility, users write to the Operations Register, LDOR and WR; this action.

performed after a hardware reset, or in the Base mode, initiates AT/EISA mode. AT/EISA mode can also be entered from Special mode by loading the Operations Register with (0 X 0 0 X 0 X X), setting Mode Select to a logic 0, disabling MOEN1 and MOEN2, and causing SRST to be active. Then a read of the Control Register address sets the device into AT/EISA mode. The DS outputs are replaced with the DSEL and MOEN signals buffered from the Operations Register, DMAEN and SRST are supported and compatible with the current BIOS. RWC pin function is now RPM so that users with two-speed drives may reduce spindle speed from a nominal 360 revolutions per minute to 300 revolutions per minute when active low. It can also be used to reduce write current when a slower data rate is selected for a given drive. Figure 9-1 illustrates the relationship among the three modes.

FIGURE 9-1. FLOW DIAGRAM BASE, SPECIAL & AT/EISA MODES

1/2

11/18/91 26-21

#### 10.0 POLLING ROUTINE

After any reset the WD37C65C, (a hard RST or soft SRST), will automatically go into a Polling routine. In between commands (and between step pulses in the SEEK Command), the WD37C65C polls all four FDDs looking for a change in the Ready line from any of the drives. Since the drive is always presumed Ready, an interrupt will only be generated following a reset. This occurs because a reset forces Not Ready status, which then promptly becomes Ready. Note that in Special, AT/EISA modes, if DMAEN is not valid 1 ms after reset goes inactive, then IRQ may be al-

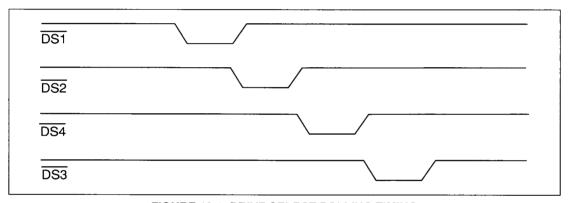

ready set and pending when finally enabled onto the bus. The polling of the Ready line by the WD37C65C occurs continuously between commands. Each drive is polled every 1.024 ms, except during the READ/WRITE commands. For mini-floppies, the polling rate is 2.048 ms. The drive polling sequence is 1-2-4-3. Note that in the AT/EISA mode, the user will not see the polling at the Drive Select signals. Figure 10-1 illustrates the Drive Select Polling Timing.

FIGURE 10-1. DRIVE SELECT POLLING TIMING

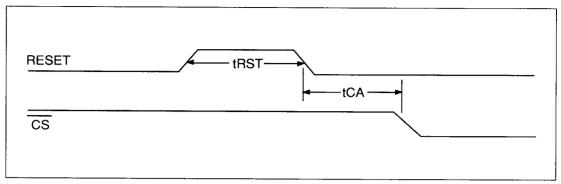

## 11.0 DEVICE RESETS

The WD37C65C supports both hardware reset (RST) pin (19) and a software reset (SRST) through use of the Operations Register. The RST pin will cause a device reset for the active duration. RST causes a default to Base mode, and selects 250 Kb MFM (or 125 Kb FM, code dependent) as the data rate (16 MHz input clock). The default data rate for a 32 MHz input clock is 500 Kb MFM. SRST will reset the microcontroller as did the RST, but will not affect the current data rate selection or the mode. RST, when active, will disable the high current driver outputs to the disk

drive. RST and SRST will not affect the values set for the internal timers - HUT, HTL, and SRT.

If the XTAL oscillators are used, instead of the TTL driven clock inputs, the hardware RST active time requirement will be extended. The oscillator circuit is designed so that RST will bootstrap the circuit into guaranteed oscillation in a fixed amount of time. The extended reset time allows the growth of the oscillation to produce stable internal clock timing.

11/18/91

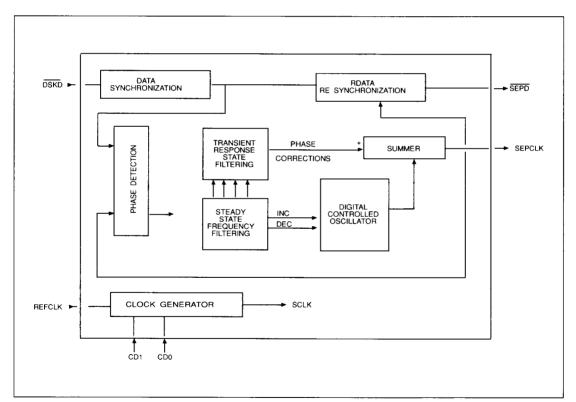

## 12.0 DATA SEPARATOR

The Data Separator is a WD92C32 Digital Phase Lock Loop Floppy Disk Data Separator (DPLL). It was designed to address high performance error rates on floppy disk drives, and to provide superior performance in terms of available bit jitter tolerance. It contains the necessary logic to achieve classical 2nd order, type 2, phase locked

loop performance. Figure 3-1 illustrates the WD92C32 used as the Data Separator in the WD37C65C system. Figure 13-1 illustrates the WD92C32 simplified block diagram. The bit jitter tolerance for the data separator is 60%, which guarantees an error rate of <10E-9.

## 13.0 WRITE PRECOMPENSATION

The WD37C65C maintains the standard first level algorithm to determine when write precompensation should be applied. The EARLY and LATE signals are used internally to select the appropriate delay in the write data pulse stream. The encoded WRITE DATA signal is synchronized to the 16 MHz or 32 MHz clock if this is the frequency on CLK1 pin (23), and clocked through a shift register. Signals EARLY, NOM, and LATE determine the amount of delay through the shift register before a multiplexer gates the chosen bit to the output. The output data pulse width has a 25% duty cycle, i.e., one fourth of the bit cell period, and equal to one half the WCLK period.

When PCVAL pin (24) = 1, all data will be precompensated by  $\pm$  125 ns, regardless of track number and data rate. However, this is only for MFM en-

coding. There is no write precompensation for FM. If PCVAL = 0, and if a track inside number 28 is accessed, then  $\pm$  187 ns precompensation will be generated. For frequencies other than 16 MHz or 32 MHz on the CLK1 pin, the precompensation values will be two and three clock cycles respectively.

When the non-standard 300 Kb/s data rate using CLK2 is chosen, the MFM precompensation will always be two clock cycles. For 9.6 MHz, this is  $\pm$  208 ns. In this case, the PCVAL function is disabled.

Write precompensation can be disabled by bit 2 of the Control Register for the AT/EISA. The PCVAL input to WD37C65C is ignored if there is no write precompensation.

FIGURE 13-1. WD92C32 SIMPLIFIED BLOCK DIAGRAM

**%**

## 14.0 CLOCK GENERATION

This logical block provides all the clocks needed by the WD37C65C. They are: Sampling Clock (SCLK), Write Clock (WCLK), and the Master Clock (MCLK).

SCLK drives the WD92C32 Data Separator used during data recovery. This clock's frequency is always 32 times the selected data rate.

WCLK is used by the encoder logic to place MFM or FM on the serial WD-stream to the disk. WCLK always has a frequency two times the selected data rate.

MCLK is used by the microsequencer. MCLK and MCLK clock all latches in a two-phase scheme. One microinstruction cycle is four MCLK cycles. MCLK has a frequency equal to eight times the selected MFM data rate or 16 times the FM data rate. Table 14-1 presents the Clock Data Rate.

Figure 14-1 illustrates the XTAL oscillator circuits for the 44-pin PLCC configuration.

In power down mode the XTAL oscillator and the clock circuitry are turned off.

| DATA<br>RATE | CODE | SCLK<br>MHz | MCLK<br>MHz | WCLK    |

|--------------|------|-------------|-------------|---------|

| 1 Mb/s       | MFM  | 32.0        | 8.0         | 2.0 MHz |

| 500 kb/s     | MFM  | 16.0        | 4.0         | 1.0 MHz |

| 500 kb/s     | FM   | 16.0        | 8.0         | 1.0 MHz |

| 250 kb/s     | FM   | 8.0         | 4.0         | 500 KHz |

| 250 kb/s     | MFM  | 8.0         | 2.0         | 500 KHz |

| 125 kb/s     | FM   | 4.0         | 2.0         | 250KHz  |

| 300 kb/s     | MFM  | 9.6         | 2.4         | 600 KHz |

**TABLE 14-1. CLOCK DATA RATE**

FIGURE 14-1. CRYSTAL OSCILLATOR CIRCUITS FOR 44-PIN PLCC

1/2

## 15.0 COMMAND PARAMETERS

The WD37C65C is capable of performing 15 different commands. Each command is initiated by a multibyte transfer from the processor. The results after execution of the command may also be a multibyte transfer back to the processor. The commands consist of three phases: Command phase, Execution phase, and the Result phase.

**Command phase** - The Floppy Disk Controller (FDC) receives all information required to perform a particular operation from the processor

**Execution phase** - The FDC performs the operation it was instructed to do.

**Result phase** - After completion of the operation, status and other housekeeping information are made available to the processor.

Table 15-1 lists the 15 WD37C65C commands.

READ DATA

READ DELETED DATA

WRITE DATA

WRITE DELETED DATA

READ A TRACK

READ ID

FORMAT A TRACK

SCAN EQUAL

SCAN LOW OR EQUAL

SCAN HIGH OR EQUAL

RECALIBRATE

SENSE INTERRUPT STATUS

SPECIFY

SENSE DRIVE STATUS

SEEK

### TABLE 15-1, WD37C65C COMMANDS

Tables 15-1 through 15-16 are presented to show the required parameters and results for each command. Most commands require nine command bytes and return seven bytes during the result phase. The "W" to the left of each byte indicates a command phase byte to be written. An "R" indicates a result byte.

| PHASE     | R/W                             | D7                                        | D6                               | D5                                        | D4                                       | D3                                       | D2                                        | D1                               | D0                                         | REMARKS                                                                                                                     |

|-----------|---------------------------------|-------------------------------------------|----------------------------------|-------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------|----------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| COMMAND   | W<br>W<br>W<br>W<br>W           | MT<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL |                                  | SK<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL | 1<br>HS<br>C<br>H<br>R<br>N<br>EOT<br>GPL |                                  | 0<br>US0<br>C<br>H<br>R<br>N<br>EOT<br>GPL | Command Codes  Sector ID information prior to command execution. The four bytes are compared against header on floppy disk. |

| EXECUTION |                                 |                                           |                                  |                                           |                                          |                                          |                                           |                                  |                                            | Data transfer between FDD and main system.                                                                                  |

| RESULTS   | R<br>R<br>R<br>R<br>R<br>R<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R          | ST0<br>ST1<br>ST2<br>C<br>H<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R          | ST0<br>ST1<br>ST2<br>C<br>H<br>R         | ST0<br>ST1<br>ST2<br>C<br>H<br>R         | ST0<br>ST1<br>ST2<br>C<br>H<br>R          | ST0<br>ST1<br>ST2<br>C<br>H<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R           | Status information after command execution.  Sector ID information after command execution.                                 |

**TABLE 15-2. READ DATA**

| PHASE     | R/W                        | D7                                               | D6                                               | D5                                               | D4                                              | D3                                              | D2                                               | D1                               | D0                                                | REMARKS                                                                                                                     |

|-----------|----------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|----------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| COMMAND   | \$\$\$\$\$\$\$\$\$\$       | MT<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | MF<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | SK<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 1<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 1<br>HS<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL |                                  | 0<br>US0<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | Command Codes  Sector ID information prior to command execution. The four bytes are compared against header on floppy disk. |

| EXECUTION |                            |                                                  |                                                  |                                                  |                                                 |                                                 |                                                  |                                  |                                                   | Data transfer between FDD and main system.                                                                                  |

| RESULTS   | R<br>R<br>R<br>R<br>R<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                | ST0<br>ST1<br>ST2<br>C<br>H<br>R                | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R                  | Status information after command execution.  Sector ID information after command execution.                                 |

**TABLE 15-3. READ DELETED DATA**

| PHASE     | R/W                        | D7                                               | D6                                               | D5                                              | D4                                              | D3                                              | D2                                               | D1                                                | D0                               | REMARKS                                                                                                                     |

|-----------|----------------------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|---------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| COMMAND   | >>                         | MT<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | MF<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 0<br>X<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 1<br>HS<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL | 0<br>US1<br>C<br>H<br>R<br>N<br>EOT<br>GPL<br>DTL |                                  | Command Codes  Sector ID information prior to command execution. The four bytes are compared against header on floppy disk. |

| EXECUTION |                            |                                                  |                                                  |                                                 |                                                 |                                                 |                                                  |                                                   |                                  | Data transfer between FDD and main system.                                                                                  |

| RESULTS   | R<br>R<br>R<br>R<br>R<br>R | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                | ST0<br>ST1<br>ST2<br>C<br>H<br>R                | ST0<br>ST1<br>ST2<br>C<br>H<br>R                | ST0<br>ST1<br>ST2<br>C<br>H<br>R                 | ST0<br>ST1<br>ST2<br>C<br>H<br>R                  | ST0<br>ST1<br>ST2<br>C<br>H<br>R | Status information after command execution.  Sector ID information after command execution.                                 |

|           | R                          | N                                                | N                                                | N                                               | N                                               | Ν                                               | N                                                | N                                                 | N                                |                                                                                                                             |

**TABLE 15-4. WRITE DATA**

| PHASE     | R/W                                    | <b>D</b> 7             | D6                     | D5                     | D4                     | D3                     | D2                     | D1                     | D0                     | REMARKS                                                                               |

|-----------|----------------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------------------------------------------------------------------------|

| COMMAND   | W<br>W                                 | MT<br>X                | MF<br>X                | 0<br>X                 | 0<br>X                 | 1<br>X                 | 0<br>HS                | 0<br>US1               | 1<br>US0               | Command Codes                                                                         |

|           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | C<br>H<br>R<br>N       | C<br>H<br>R<br>N       | C<br>H<br>R<br>N       | C<br>H<br>R<br>N       | C<br>H<br>R<br>N       | C<br>H<br>R<br>N       | C<br>H<br>R            | C<br>H<br>R            | Sector ID information prior to command execution. The four bytes are compared against |

|           | W<br>W<br>W                            | EOT<br>GPL<br>DTL      | EOT<br>GPL<br>DTL      | EOT                    | EOT                    | EOT                    | EOT                    | N<br>EOT<br>GPL<br>DTL | N<br>EOT<br>GPL<br>DTL | header on floppy disk.                                                                |

| EXECUTION |                                        |                        |                        |                        |                        |                        |                        |                        |                        | Data transfer between FDD and main system.                                            |

| RESULTS   | R<br>R<br>R                            | ST0<br>ST1<br>ST2<br>C | Status information after command execution.                                           |

|           | R<br>R<br>R                            | H<br>R<br>N            | Sector ID information after command execution.                                        |

**TABLE 15-5. WRITE DELETED DATA**

| PHASE     | R/W | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | REMARKS                                                                                      |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------------------------------------------------------------------|

| COMMAND   | W   | 0   | MF  | SK  | 0   | 0   | 0   | 1   | 0   | Command Codes                                                                                |

|           | W   | X   | X   | X   | X   | X   | HS  | US1 | US1 |                                                                                              |

|           | W   | С   | С   | С   | С   | С   | С   | С   | С   | Sector ID information prior to                                                               |

|           | W   | Η   | Н   | Н   | Н   | Н   | Н   | H   | Н   | command execution.                                                                           |

|           | W   | R   | R   | R   | R   | R   | R   | R   | R   |                                                                                              |

|           | W   | N   | N   | N   | N   | N   | Ν   | N   | N   |                                                                                              |

|           | W   | EOT |                                                                                              |

|           | W   | GPL |                                                                                              |

|           | W   | DTL |                                                                                              |

| EXECUTION |     |     |     |     |     |     |     |     |     | Data transfer between FDD and main system. FDD reads all data fields from index hole to EOT. |

| RESULTS   | R   | ST0 | Status information after com-                                                                |

|           | R   | ST1 | mand execution.                                                                              |

|           | R   | ST2 |                                                                                              |

|           | R   | С   | С   | С   | С   | С   | С   | С   | С   |                                                                                              |

|           | R   | H   | Н   | H   | Н   | Н   | H   | Н   | Н   | Sector ID information after com-                                                             |

|           | R   | R   | R   | R   | R   | R   | R   | R   | R   | mand execution                                                                               |

|           | R   | N   | N   | N   | N   | N   | N   | Ν   | N   |                                                                                              |

**TABLE 15-6. READ A TRACK**

1/2

11/18/91

| PHASE     | R/W         | D7                     | D6                     | D5                     | D4                     | D3                     | D2                     | D1                     | D0                     | REMARKS                                                                      |

|-----------|-------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------------------------------------------------------------|

| COMMAND   | W<br>W      | 0<br>X                 | MF<br>X                | 0<br>X                 | 0<br>X                 | 1<br>X                 | 0<br>HS                | 1<br>US1               | 0<br>US0               | Command Codes                                                                |

| EXECUTION |             |                        |                        |                        |                        |                        |                        |                        |                        | The first correct ID information on the cylinder is stored in Data Register. |