- Welcome to AK Laboratory.

AK Laboratory

место для общения

Последние сообщения

#1

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от Slabovik - Сегодня в 23:02nOE... я забыл про него.

RDY - это не оно. Это строб, по фронту которого происходит перезапись данных из регистра сдвига в выходной регистр.

Тогда да, nOE пусть остаётся как есть. Потому что выход надо "погасить" перед подъёмом RDY и "зажечь" после выставления строки AB.

Гм, оборванный вывод? Это вполне проблема, да... Жаль, что у STM даташиты такие разбросанные. Не случилось ли какой рестрикции из-за конфигов. Но это читать много надо, так не помню, практиковался совсем мало

Ну трындец какой-то. Я тутпро RDY вещаю, а на входе матрицы этой фигни нет. В общем, RDY - это ST на микросхемах, формируется как-то автоматом. Давай я завтра, как время будет, возьму и на основе уже этой схемы нарисую циклограммы, как там вообще должно быть. А то я по памяти всё, и... промахиваюсь...

и,да... OE по схеме не задействован, так что совсем печалька...

RDY - это не оно. Это строб, по фронту которого происходит перезапись данных из регистра сдвига в выходной регистр.

Тогда да, nOE пусть остаётся как есть. Потому что выход надо "погасить" перед подъёмом RDY и "зажечь" после выставления строки AB.

Гм, оборванный вывод? Это вполне проблема, да... Жаль, что у STM даташиты такие разбросанные. Не случилось ли какой рестрикции из-за конфигов. Но это читать много надо, так не помню, практиковался совсем мало

Ну трындец какой-то. Я тутпро RDY вещаю, а на входе матрицы этой фигни нет. В общем, RDY - это ST на микросхемах, формируется как-то автоматом. Давай я завтра, как время будет, возьму и на основе уже этой схемы нарисую циклограммы, как там вообще должно быть. А то я по памяти всё, и... промахиваюсь...

и,да... OE по схеме не задействован, так что совсем печалька...

#2

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от zenon - Сегодня в 22:36RDY это nOE? Который шимить можно?

Тут понял что у меня происходит, PA15, я его и так и эдак - не вижу, как был высоким так и остаётся высоким....

... ну и перекиул сначала на PA6, - и сразу увидел его анализатором, завёл на enable, вижу оба состояния.

перекинул инит на PB15, чтобы себя проверить, не напутал ли я что-то с кодом, нет всё ок, рабодает.

В что с PA15 не пойму, те же манипуляции с ним - не реагирует никак, козы на плате нет, до своей ноги звонится.

Может и до этого была проблема из-за него.

Тут понял что у меня происходит, PA15, я его и так и эдак - не вижу, как был высоким так и остаётся высоким....

... ну и перекиул сначала на PA6, - и сразу увидел его анализатором, завёл на enable, вижу оба состояния.

перекинул инит на PB15, чтобы себя проверить, не напутал ли я что-то с кодом, нет всё ок, рабодает.

В что с PA15 не пойму, те же манипуляции с ним - не реагирует никак, козы на плате нет, до своей ноги звонится.

Может и до этого была проблема из-за него.

#3

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от Slabovik - Сегодня в 21:30При инициализации устанавливаем RDY (OE? не помню, как там на картинке) в 1, Clk тоже в 1

При передаче

1. Опускаем RDY

2. запускаем SPI (для одной строки 32x16 надо передать (32/8)*(16/4)=16 байт. Если передать меньше, то строка не обновится полностью - переданное ранее просто сместится далее по регистрам. Байты можно придумать разные, хоть 1-2-3-4-5...

3.a Поднимаем RDY

3.б Выставляем строку AB

Эти два действия надо сделать с минимальным интервалом времени, причём порядок даже не важен. Если разнести во времени, то между этими действиями выведенные данные светятся на "чужой" строке, а это нам сейчас не надо (можно загонять конечно между делом 16 нулей, либо "жать резет", но это не сейчас).

Далее перво-наперво, посмотри осциллографом, как выглядит Clk.

Далее можно зацепить каналы на Rdy и Data. Синхронизацию на Rdy прицепить по спаду - на экране будет начало посылки. Прицепить по подъёму - будет конец посылки. Ну там разберёшься...

При передаче

1. Опускаем RDY

2. запускаем SPI (для одной строки 32x16 надо передать (32/8)*(16/4)=16 байт. Если передать меньше, то строка не обновится полностью - переданное ранее просто сместится далее по регистрам. Байты можно придумать разные, хоть 1-2-3-4-5...

3.a Поднимаем RDY

3.б Выставляем строку AB

Эти два действия надо сделать с минимальным интервалом времени, причём порядок даже не важен. Если разнести во времени, то между этими действиями выведенные данные светятся на "чужой" строке, а это нам сейчас не надо (можно загонять конечно между делом 16 нулей, либо "жать резет", но это не сейчас).

Далее перво-наперво, посмотри осциллографом, как выглядит Clk.

Далее можно зацепить каналы на Rdy и Data. Синхронизацию на Rdy прицепить по спаду - на экране будет начало посылки. Прицепить по подъёму - будет конец посылки. Ну там разберёшься...

#4

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от zenon - Сегодня в 20:57Да, вероятно скорость выше, анализатор обычный на стм-ке 24МГц может максимум.

---

У меня таки оно ожило, но пока не так как надо, потому что метод не тот, ну и передаю я всего одну посылку 8-бит, а надо 16.

Сейчас над распутать алгоритм передачи.

Из вышеупомянутой ссылки он такой:

дальше вопрос в SPI, настроил на 8-ми битный режим, main такой:

https://youtu.be/fBkpjaoDfQo

:: добавлено 01 Май, 2024, 20:07

ы. Да, без RDY (MISO) каша, надо попробовать третий провод и нормально посмотреть.

---

У меня таки оно ожило, но пока не так как надо, потому что метод не тот, ну и передаю я всего одну посылку 8-бит, а надо 16.

Сейчас над распутать алгоритм передачи.

Из вышеупомянутой ссылки он такой:

Цитата1. Выдаём по SPI данные для сдвиговых регистров.Для переключения PinA-PinB сделал функцию:

2. Устанавливаем лог. 0 на ножке nOE.

3. Устанавливаем лог. уровни на ножках A и B в соответствии с обновляемой группой светодиодов (одной из четырёх).

4. Выдаём на ножку SCLK короткий положительный импульс.

5. Устанавливаем лог. 1 на ножке nOE.

void PINAB_change(uint8_t col){

switch (col) {

case 0: {PinA0; PinA0;};

case 1: {PinA0; PinA1;};

case 2: {PinA1; PinA0;};

case 3: {PinA1; PinA1;};

}

}дальше вопрос в SPI, настроил на 8-ми битный режим, main такой:

do {

uint8_t _data = 0; // то, что запишем в SPI

for (col = 0; col < 4; col++) {

SPI1_send(_data); // 1. передаём данные

nOE0; // 2. Устанавливаем лог. 0 на ножке nOE

PINAB_change(col); // лог. уровни на ножках A и B

SCLK1; // 3. выдаём на ножку SCLK короткий положительный импульс

dummy_loop(10);

SCLK0;

nOE1;

}

delay_ms(10);

} while (1);

}

https://youtu.be/fBkpjaoDfQo

:: добавлено 01 Май, 2024, 20:07

ы. Да, без RDY (MISO) каша, надо попробовать третий провод и нормально посмотреть.

#5

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от Slabovik - Сегодня в 20:11Видишь лес. А надо смотреть деревья. Пакеты идут много быстрее, чем настроен анализатор. В итоге весь пакет выглядит иголкой. В итоге ничего не видно.

Я не особо разбирался в инитах, но на какой скорости там должно ходить всё? Для разборок не стоит делать высокую скорость, не более мегагерца, а лучше ниже.

И ещё. Там есть третий сигнал. Его тоже надо бы смотреть. Он очень помогает в разборках, если настроен правильно: перед передачей строки его надо опустить, а по окончании поднять, чем переданная информация (строка) будет передана на выход регистров.

Попробуй описывать словами, что именно делаешь. Т.е "настраиваем таймер SPI на такую-то скорость... поднимаем RDY...опускаем......

В общем, clk должен быть похож на меандр, примерно. Data - как попадёт, но меняется реже. Rdy - перед пакетом падает, после поднимается. Скорость передачи контролируется по clk

зы: а может ли анализатор вообще с такой скоростью работать, с какой контроллер выдаёт? В этом случае лучше осциллограф.

Я не особо разбирался в инитах, но на какой скорости там должно ходить всё? Для разборок не стоит делать высокую скорость, не более мегагерца, а лучше ниже.

И ещё. Там есть третий сигнал. Его тоже надо бы смотреть. Он очень помогает в разборках, если настроен правильно: перед передачей строки его надо опустить, а по окончании поднять, чем переданная информация (строка) будет передана на выход регистров.

Попробуй описывать словами, что именно делаешь. Т.е "настраиваем таймер SPI на такую-то скорость... поднимаем RDY...опускаем......

В общем, clk должен быть похож на меандр, примерно. Data - как попадёт, но меняется реже. Rdy - перед пакетом падает, после поднимается. Скорость передачи контролируется по clk

зы: а может ли анализатор вообще с такой скоростью работать, с какой контроллер выдаёт? В этом случае лучше осциллограф.

#6

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от zenon - Сегодня в 17:08Накидал инит SPI для F1, дефайны для вкл/выкл пинов.

Подключил анализатор на CLK и MOSI, передаю единичку, вижу ... не пойму что вижу???

скрины с анализатора и код тут

https://github.com/minamonra/my_stm_snippets/tree/main/F1/p10m

Подключил анализатор на CLK и MOSI, передаю единичку, вижу ... не пойму что вижу???

скрины с анализатора и код тут

https://github.com/minamonra/my_stm_snippets/tree/main/F1/p10m

#7

Фото, видео, аудио / Re: Коротко о погоде

Последний ответ от Slabovik - Вчера в 08:17Снова прожарило до +28. И снова затем стало прохладно. Качели температурные. Но зато в конце прожарки случился дождь с громом и молнией.

#8

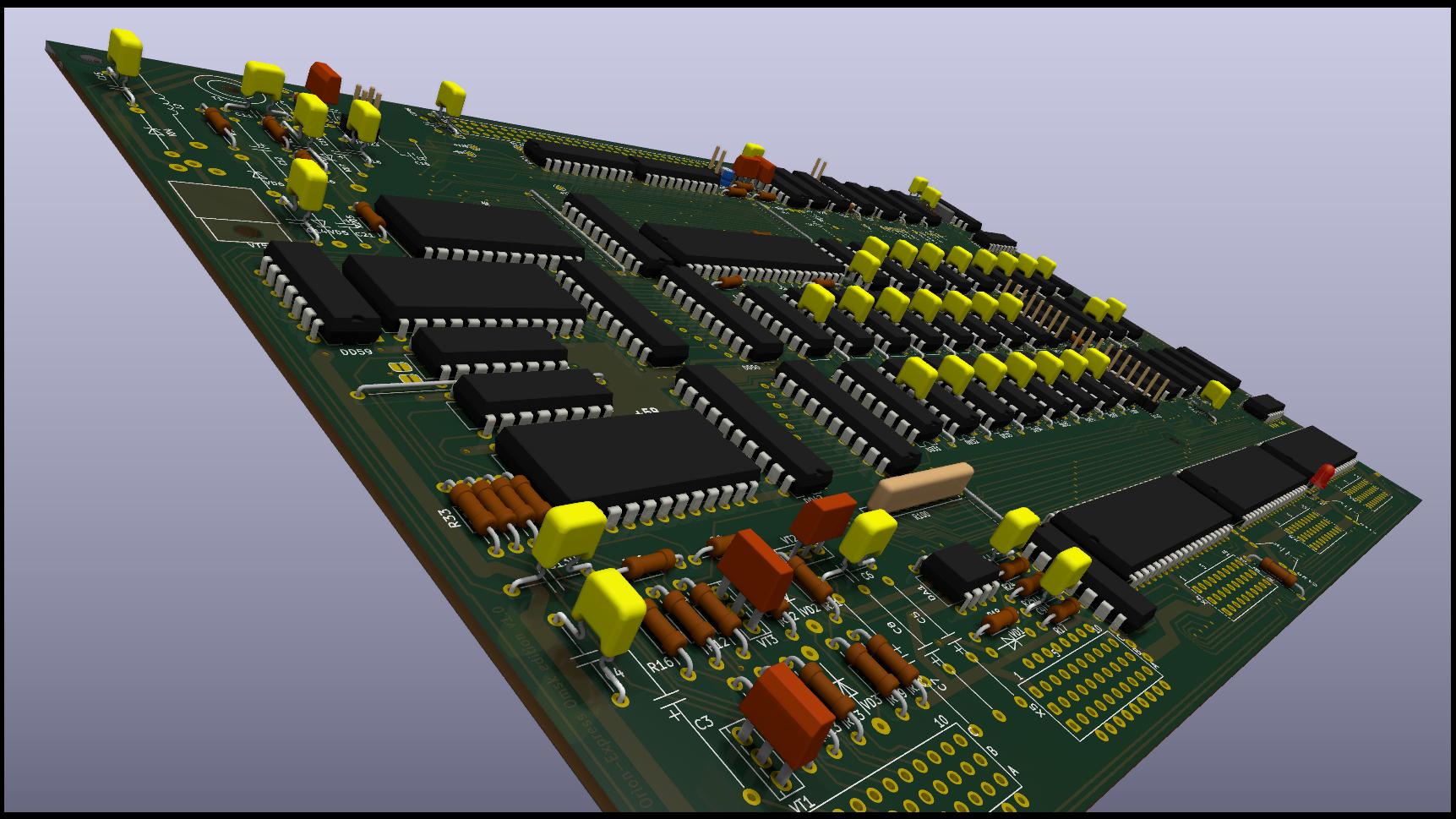

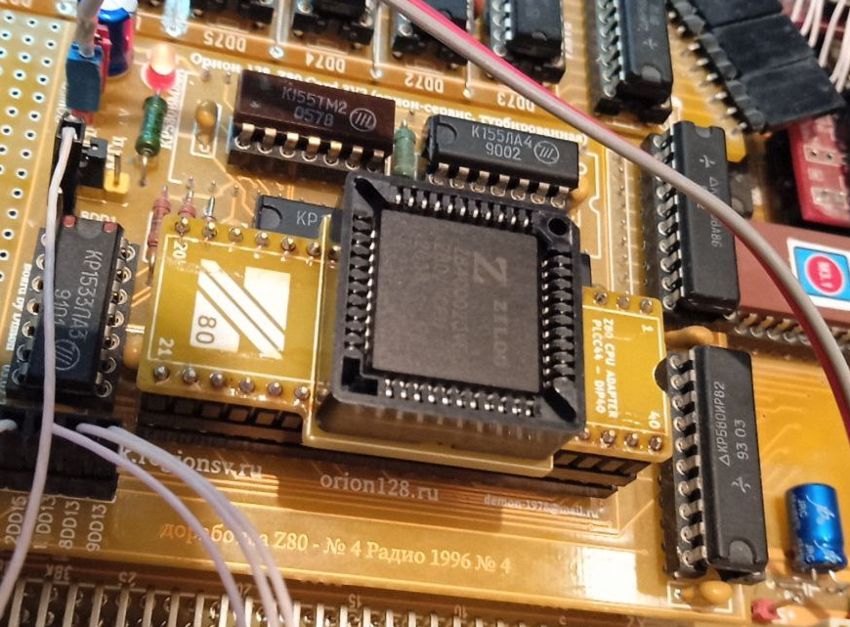

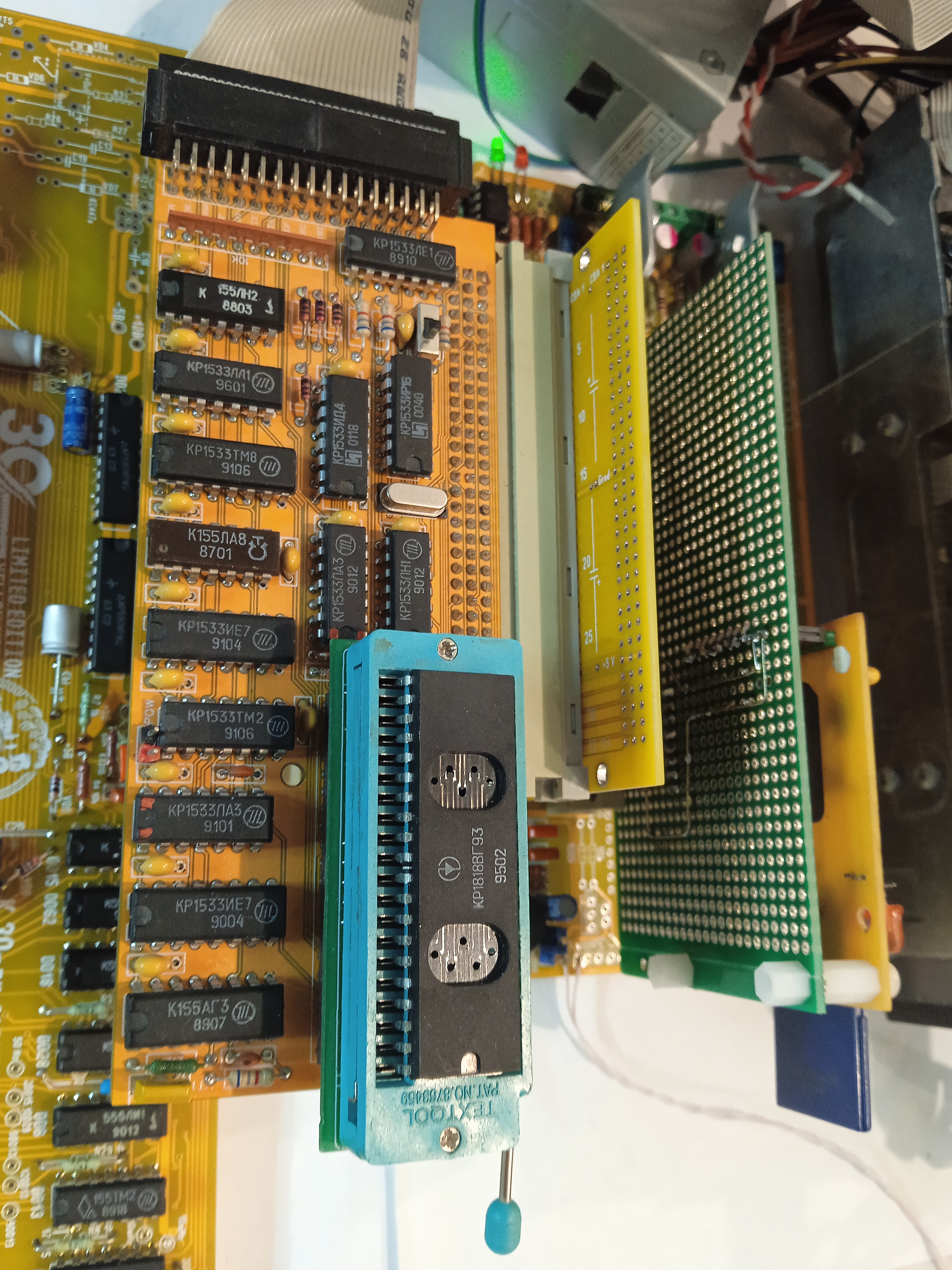

Цифровая техника / Re: Орион-128 возрождение эпох...

Последний ответ от matrixplus - 29 Апр., 2024, 12:18

процессор z80 в орионе http://rdk.regionsv.ru/orion128z80test/z-001.jpg

:: добавлено 29 Апр., 2024, 12:23

Кросшина + кросшина мини http://rdk.regionsv.ru/orion512/cros/cros-017.jpg

и вставленный НГМД

:: добавлено Вчера в 00:18

Ром диск на 27с512 - 27с801 http://rdk.regionsv.ru/orion512/rom-001.jpg

Описание и сборка http://rdk.regionsv.ru/orion128-express-05-01.htm

#9

Цифровая техника / Re: Re: Орион-128 возрождение ...

Последний ответ от matrixplus - 28 Апр., 2024, 09:21 #10

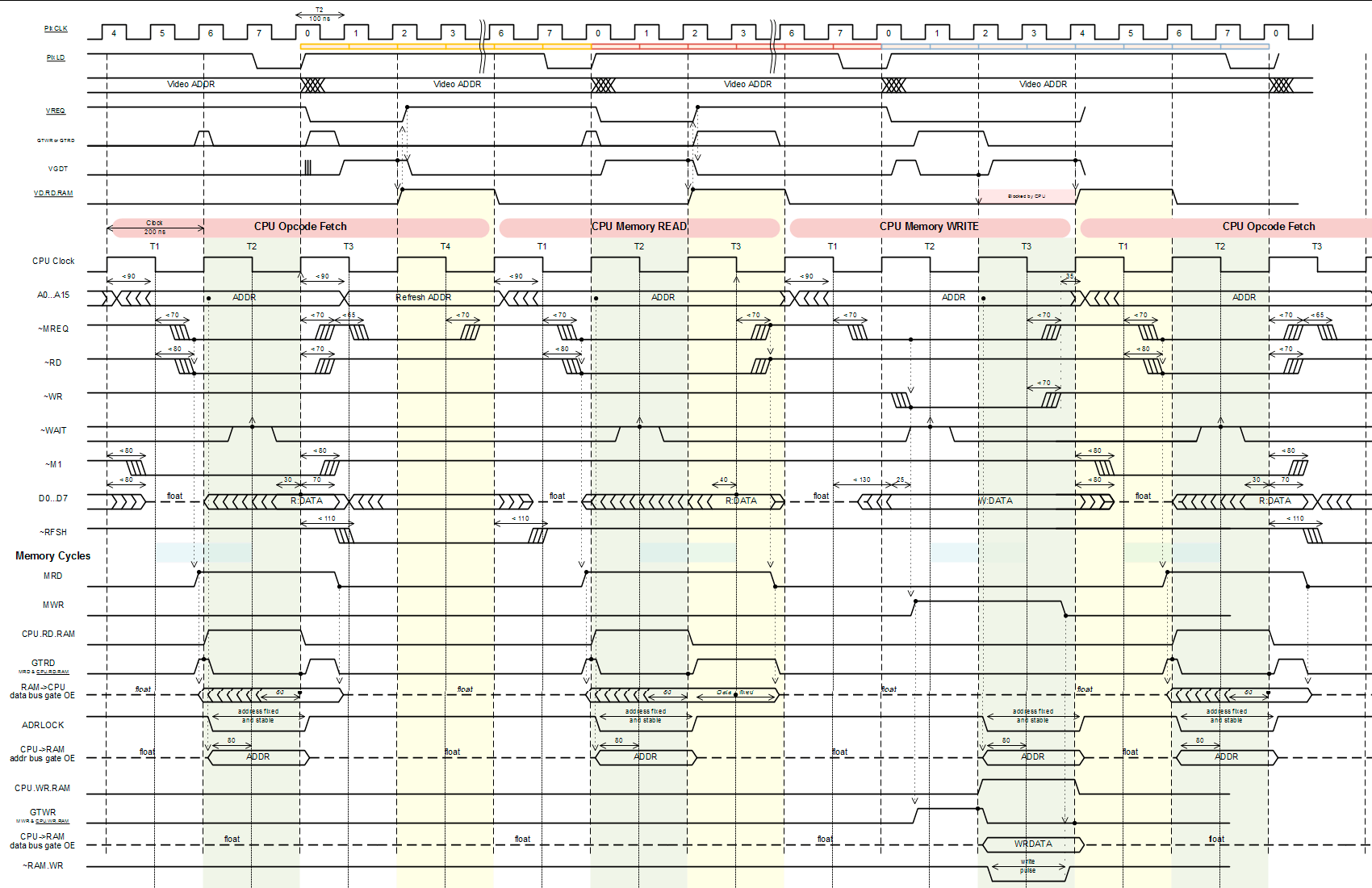

Цифровая техника / Re: Стандарты VESA: как сгенер...

Последний ответ от Slabovik - 27 Апр., 2024, 14:06Наткнулся на интересные штуки.

Дисплей 480x272 с параллельным интерфейсом

Winstar_WF43VTIAEDNN0_480x272_TFT.pdf

Пока вроде ничего интересного. Но посмотрим на контроллер

ST7282_480x272_RGB.pdf

Сразу скажу, что смотреть можно со страницы 54 - там самое интересное.

Для ленивых скажу, что фишка в том, что этот RGB - обычный 24-битный параллельный интерфейс для динамического обновления изображения панели. Ну т.е. работает практически как телевизор - подаёшь поток кадров, разбитых на строки - изображение есть. Пиксельная частота от 9 до 12 МГц, а это значит, что можно эти индикаторы использовать в простых конструкциях, выполненных на рассыпухе. Для этого надо соорудить схему хранения изображения и её интерфейсы с контроллером и, собственно, дисплеем.

480x272 - это 130560 пикселей. Если взять по байту на пиксель (режим 256 цветов), то объём необходимой памяти совсем невелик - всего 128 килобайт. Даже если взять старый Z80 с тактовой 5МГц, принять (очень приблизительно), что на запись одного пикселя ему нужно от 6 до 10 тактов (очень сильно зависит от организации процедур, но стековые операции - это 10 тактов на 2 байта), то на заполнение экрана требуется 130560*0,2мкс= 156172 до 261120 мкс, т.е. от 0,15 до 0,26 секунды. В принципе, для всяких контроллеров мне видится приемлемым...

Да, приаттачил pdf-ку, там данные на контроллер другой конторы. У него основное отличие в другом фронте тактирования и синхримпульс ему нужен длительностью 1, а не 4. Всё остальное, как и у первого, может варьироваться в довольно широких пределах. Надо попробовать совместить/сопоставить с сигналами от самодельных бытовых ПК.

ОЗУ выполняет двоякую роль. Во-первых, это ОЗУ центрального процессора. У него доступ к нему должен быть немедленным (приоритетным) - это необходимо, чтобы исключить ожидание при коллизиях (обращению к ОЗУ более чем одного устройства одновременно).

Процессоры 8080/Z80 а также 8086 имеют особенность. К ОЗУ они обращаются не более одного раза за цикл, а циклы состоят из трёх-четырёх тактов, иногда и более. Т.е. между тактами, когда они обращаются к памяти, есть такты, в которых память может взаимодействовать с другими устройствами (экраном, ДМА).

Таким образом, экран должен получать данные для отображения каждых 4 или 8 пикселов (обычно принято . Попиксельно таскать не выйдет - нужна чрезмерно большая скорость.

. Попиксельно таскать не выйдет - нужна чрезмерно большая скорость.

Ещё одно условие, если процессор главный при доступе к памяти. Организуемые циклы памяти синхронизированы с тактами процессора. Если видеоконтроллер синхронизирован с этими тактами, то длительность показа пикселей между выборками из памяти должна составлять не менее двух тактов ЦП. Если не синхронизирован - более трёх (нужно для гарантированного перекрытия свободного цикла памяти при любом положении фронтов во времени).

Получается, для синхронизированного. Примем пиксельную частоту 10 МГц (просто для ровного счёта). 4 пикселя отображаются 400 наносекунд. Сюда должно войти 2 (3-4-5...) такта ЦП. Проще считать так: пиксельную частоту делим на пиксели за выбоку и умножаем на такты ЦП.

2 такта - это 10.4*2=5МГц тактовой частоты = 1/2 пиксельной частоты. При этом такт, он же цикл памяти, длится 200нс, что вполне комфортно.

Три такта - 7,5 МГц, 133 нс. Z80 вполне работоспособен. Синхронизировать не очень удобно, но решаемо.

Четыре такта - 10 МГц, 100 нс. Есть варианты, но надо уже применять скоростную логику и память, и если ОЗУ выборка обычно 70 нс, то с ПЗУ похуже.

Для несинхронизированного при 10 МГц пиксельной и 4 пикселях на выборку получается минимальная граница тактовой 7,5 МГц.

И Z80 и 8086 нужно брать не хуже 8-мегагерцовых версий.

А вот при 8 пикселях на выборку

10/8 *3=3,75 - 8080 с трудом, но пойдёт (изначально это 3-х мегагерцовые процы, но практика показывает, что небольшой оверклокинг допустим). 10 МГц пиксельной ведь тоже не обязательно, можно 9 (минималка для экранчиков).

В общем, самая плотная загрузка памяти - у Z80 в процессе 3-тактовых циклов. Из трёх тактов цикла один занимает ЦП. Второй - видео. Третий - а кто угодно (ДМА). Таким образом, скорость передачи через ДМА в пике может быть 1/3 тактовой ЦП, при 7,5 МГц это 2,5 мегабайта в секунду. Вполне ничего И... никто никому не мешает!

И... никто никому не мешает!

Нарисовал 8-пиксельную выборку совмещённую с 5МГц Z80.

Времянки ЦП от 6-магагерцовой версии.

Поскольку 8pix - это достаточно редко, запрос VREQ создаётся только после загрузки пикселей в регистр вывода видео. Для 4-пиксельного варианта необходимо запрос делать уже на выводе последнего пикселя, иначе следующая порция пикселей опоздает.

Да, почему 4 пикселя либо 8?

Если цвет один (монохром) - выбирать можно байт. Это и будут 8 пикселей.

Если цвета 4 - в байт можно засунуть 4 пикселя.

Если цветов 16 - в байте только два пикселя. Для минималки в 4 пикселя нужна выборка сразу двух смежных байт. Т.е. шина данных памяти становится 16-битной.

Если цветов 256, то в одном байте только один пиксель. Для выборки 4-х пикселей нужно выбрать сразу 4 байта, а это 32 бита ширины.

В общем, чем шире данные памяти, тем сложнее сделать арбитраж с шиной данных ЦП. Дело не в самой сложности, но в количестве микросхем.

Поэтому мне видится достаточно интересным при Z80 применение 128-килобайтных микросхем параллельно 4 штуки и выборки по 4 пикселя. Если 8086 - 8 штук микросхем и выборки по 8 пикселей (а чего терять? Всё-равно мегабайт насобирать надо)

Дисплей 480x272 с параллельным интерфейсом

Winstar_WF43VTIAEDNN0_480x272_TFT.pdf

Пока вроде ничего интересного. Но посмотрим на контроллер

ST7282_480x272_RGB.pdf

Сразу скажу, что смотреть можно со страницы 54 - там самое интересное.

Для ленивых скажу, что фишка в том, что этот RGB - обычный 24-битный параллельный интерфейс для динамического обновления изображения панели. Ну т.е. работает практически как телевизор - подаёшь поток кадров, разбитых на строки - изображение есть. Пиксельная частота от 9 до 12 МГц, а это значит, что можно эти индикаторы использовать в простых конструкциях, выполненных на рассыпухе. Для этого надо соорудить схему хранения изображения и её интерфейсы с контроллером и, собственно, дисплеем.

480x272 - это 130560 пикселей. Если взять по байту на пиксель (режим 256 цветов), то объём необходимой памяти совсем невелик - всего 128 килобайт. Даже если взять старый Z80 с тактовой 5МГц, принять (очень приблизительно), что на запись одного пикселя ему нужно от 6 до 10 тактов (очень сильно зависит от организации процедур, но стековые операции - это 10 тактов на 2 байта), то на заполнение экрана требуется 130560*0,2мкс= 156172 до 261120 мкс, т.е. от 0,15 до 0,26 секунды. В принципе, для всяких контроллеров мне видится приемлемым...

Да, приаттачил pdf-ку, там данные на контроллер другой конторы. У него основное отличие в другом фронте тактирования и синхримпульс ему нужен длительностью 1, а не 4. Всё остальное, как и у первого, может варьироваться в довольно широких пределах. Надо попробовать совместить/сопоставить с сигналами от самодельных бытовых ПК.

ОЗУ выполняет двоякую роль. Во-первых, это ОЗУ центрального процессора. У него доступ к нему должен быть немедленным (приоритетным) - это необходимо, чтобы исключить ожидание при коллизиях (обращению к ОЗУ более чем одного устройства одновременно).

Процессоры 8080/Z80 а также 8086 имеют особенность. К ОЗУ они обращаются не более одного раза за цикл, а циклы состоят из трёх-четырёх тактов, иногда и более. Т.е. между тактами, когда они обращаются к памяти, есть такты, в которых память может взаимодействовать с другими устройствами (экраном, ДМА).

Таким образом, экран должен получать данные для отображения каждых 4 или 8 пикселов (обычно принято

. Попиксельно таскать не выйдет - нужна чрезмерно большая скорость.

. Попиксельно таскать не выйдет - нужна чрезмерно большая скорость.Ещё одно условие, если процессор главный при доступе к памяти. Организуемые циклы памяти синхронизированы с тактами процессора. Если видеоконтроллер синхронизирован с этими тактами, то длительность показа пикселей между выборками из памяти должна составлять не менее двух тактов ЦП. Если не синхронизирован - более трёх (нужно для гарантированного перекрытия свободного цикла памяти при любом положении фронтов во времени).

Получается, для синхронизированного. Примем пиксельную частоту 10 МГц (просто для ровного счёта). 4 пикселя отображаются 400 наносекунд. Сюда должно войти 2 (3-4-5...) такта ЦП. Проще считать так: пиксельную частоту делим на пиксели за выбоку и умножаем на такты ЦП.

2 такта - это 10.4*2=5МГц тактовой частоты = 1/2 пиксельной частоты. При этом такт, он же цикл памяти, длится 200нс, что вполне комфортно.

Три такта - 7,5 МГц, 133 нс. Z80 вполне работоспособен. Синхронизировать не очень удобно, но решаемо.

Четыре такта - 10 МГц, 100 нс. Есть варианты, но надо уже применять скоростную логику и память, и если ОЗУ выборка обычно 70 нс, то с ПЗУ похуже.

Для несинхронизированного при 10 МГц пиксельной и 4 пикселях на выборку получается минимальная граница тактовой 7,5 МГц.

И Z80 и 8086 нужно брать не хуже 8-мегагерцовых версий.

А вот при 8 пикселях на выборку

10/8 *3=3,75 - 8080 с трудом, но пойдёт (изначально это 3-х мегагерцовые процы, но практика показывает, что небольшой оверклокинг допустим). 10 МГц пиксельной ведь тоже не обязательно, можно 9 (минималка для экранчиков).

В общем, самая плотная загрузка памяти - у Z80 в процессе 3-тактовых циклов. Из трёх тактов цикла один занимает ЦП. Второй - видео. Третий - а кто угодно (ДМА). Таким образом, скорость передачи через ДМА в пике может быть 1/3 тактовой ЦП, при 7,5 МГц это 2,5 мегабайта в секунду. Вполне ничего

И... никто никому не мешает!

И... никто никому не мешает!

Нарисовал 8-пиксельную выборку совмещённую с 5МГц Z80.

Времянки ЦП от 6-магагерцовой версии.

Поскольку 8pix - это достаточно редко, запрос VREQ создаётся только после загрузки пикселей в регистр вывода видео. Для 4-пиксельного варианта необходимо запрос делать уже на выводе последнего пикселя, иначе следующая порция пикселей опоздает.

Да, почему 4 пикселя либо 8?

Если цвет один (монохром) - выбирать можно байт. Это и будут 8 пикселей.

Если цвета 4 - в байт можно засунуть 4 пикселя.

Если цветов 16 - в байте только два пикселя. Для минималки в 4 пикселя нужна выборка сразу двух смежных байт. Т.е. шина данных памяти становится 16-битной.

Если цветов 256, то в одном байте только один пиксель. Для выборки 4-х пикселей нужно выбрать сразу 4 байта, а это 32 бита ширины.

В общем, чем шире данные памяти, тем сложнее сделать арбитраж с шиной данных ЦП. Дело не в самой сложности, но в количестве микросхем.

Поэтому мне видится достаточно интересным при Z80 применение 128-килобайтных микросхем параллельно 4 штуки и выборки по 4 пикселя. Если 8086 - 8 штук микросхем и выборки по 8 пикселей (а чего терять? Всё-равно мегабайт насобирать надо)