- Welcome to AK Laboratory.

AK Laboratory

место для общения

Последние сообщения

#1

Цифровая техника / Re: Запустить 8086

Последний ответ от Slabovik - Вчера в 17:30Думаю, надо пока закончить с генератором. Вот три варианта

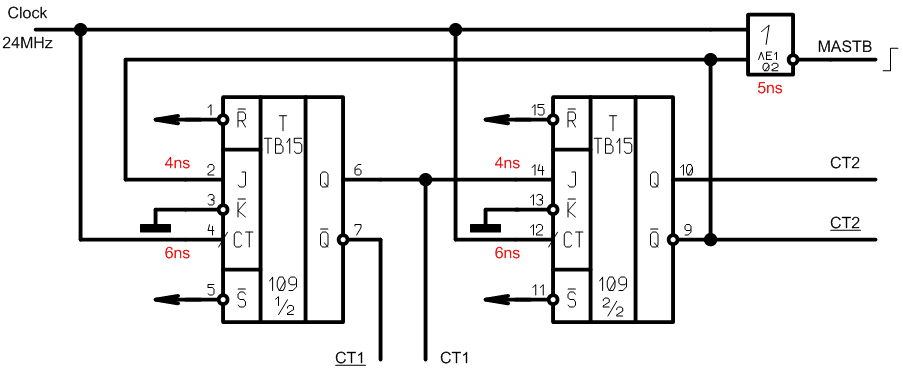

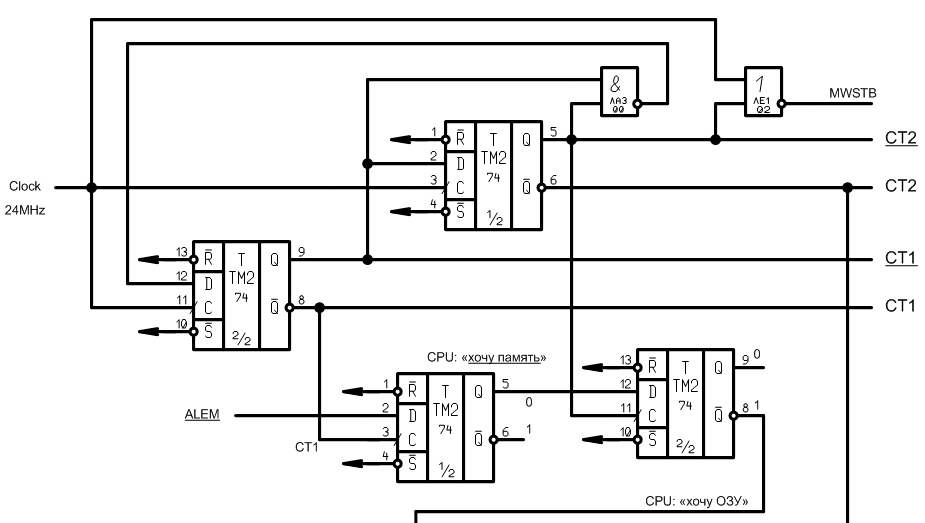

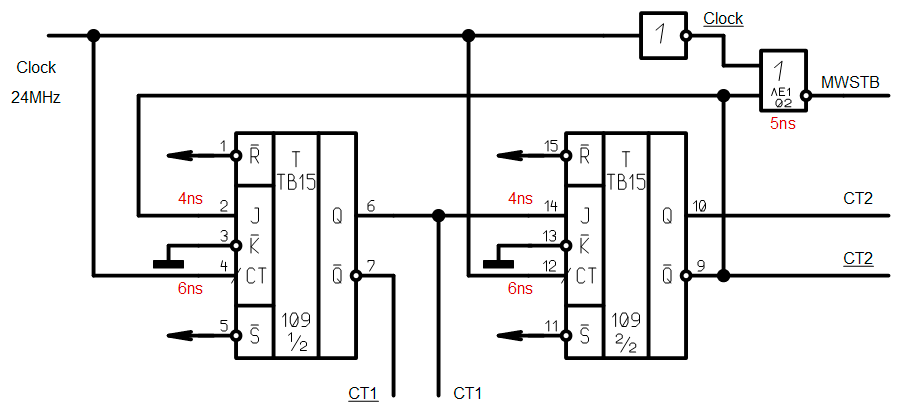

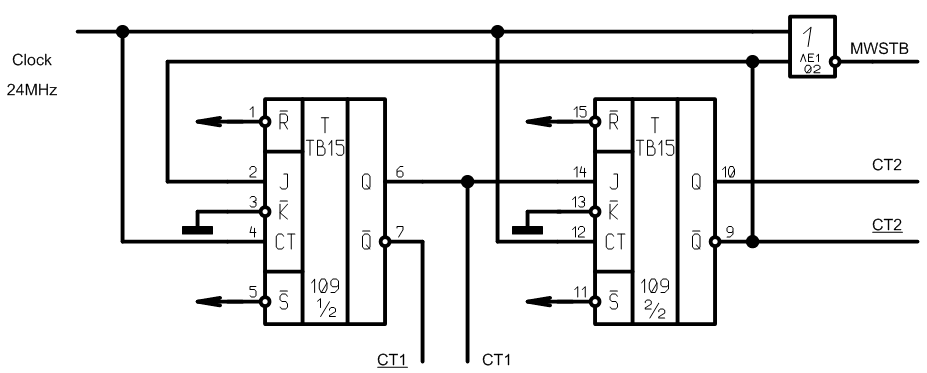

Первый - делитель на три на основе JK-триггеров

Сигнал MASTB вспомогательный, по его восходящему фронту и до конца цикла формируется сигнал MADROE (Memory ADdR Output Enable) - строб, подаваемый на регистры, содержащие адрес, подаваемый на шину RAM

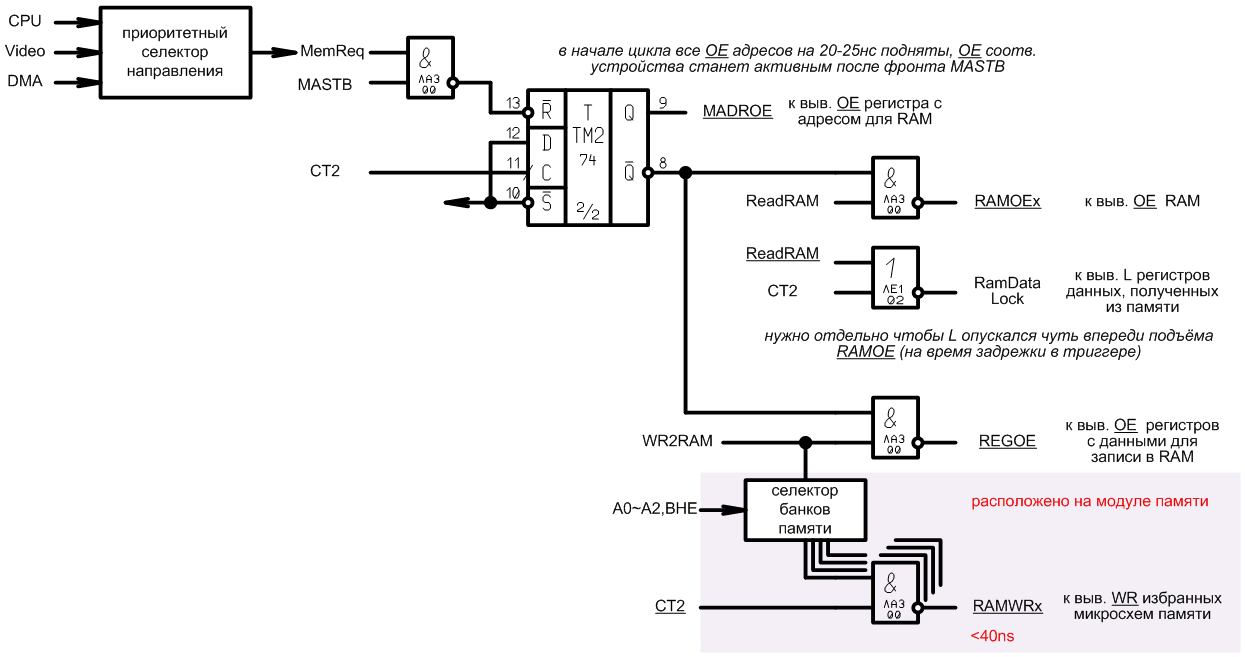

Очень примерно это может выглядеть так (схема без подробностей, только для понимания)

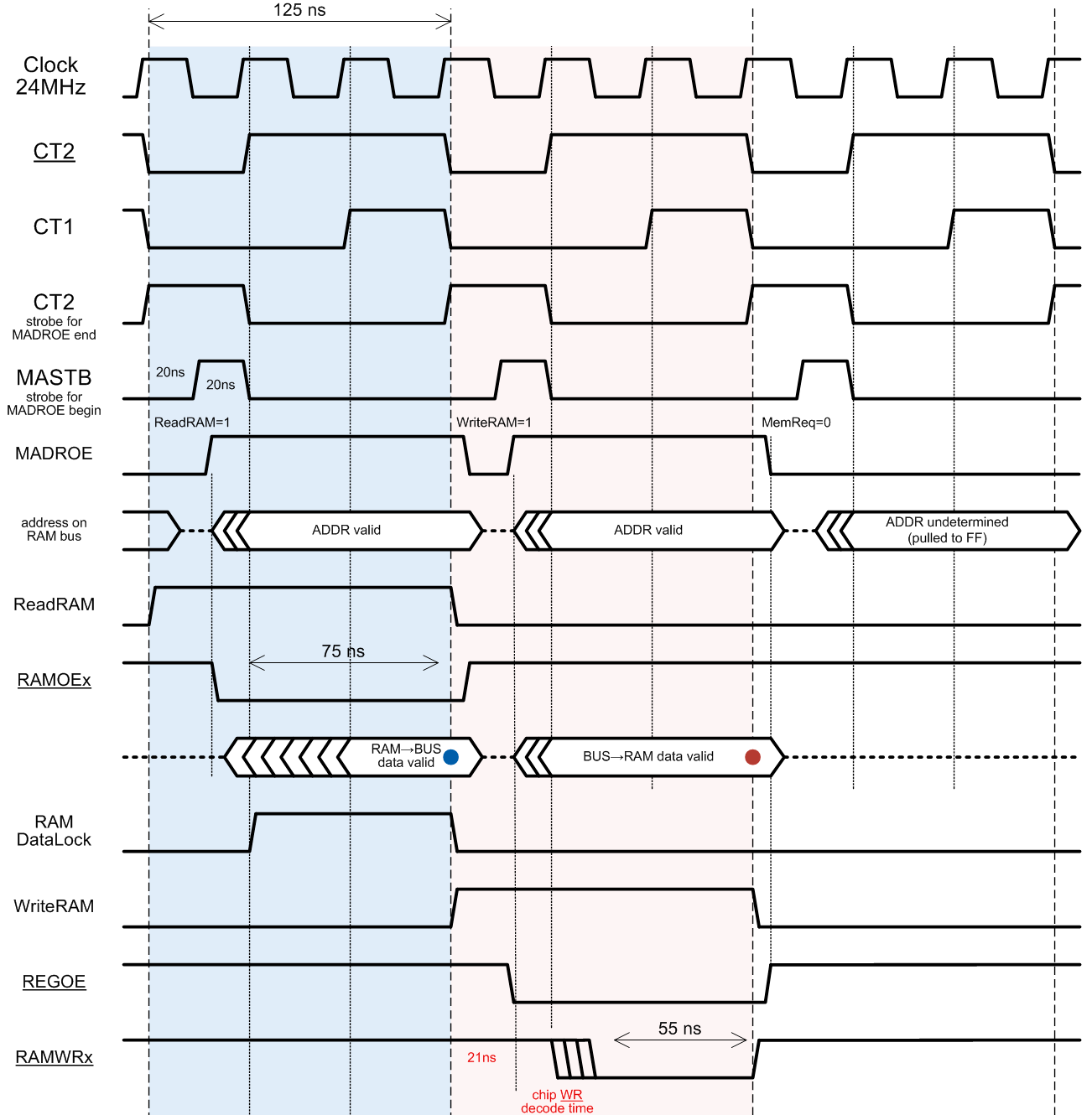

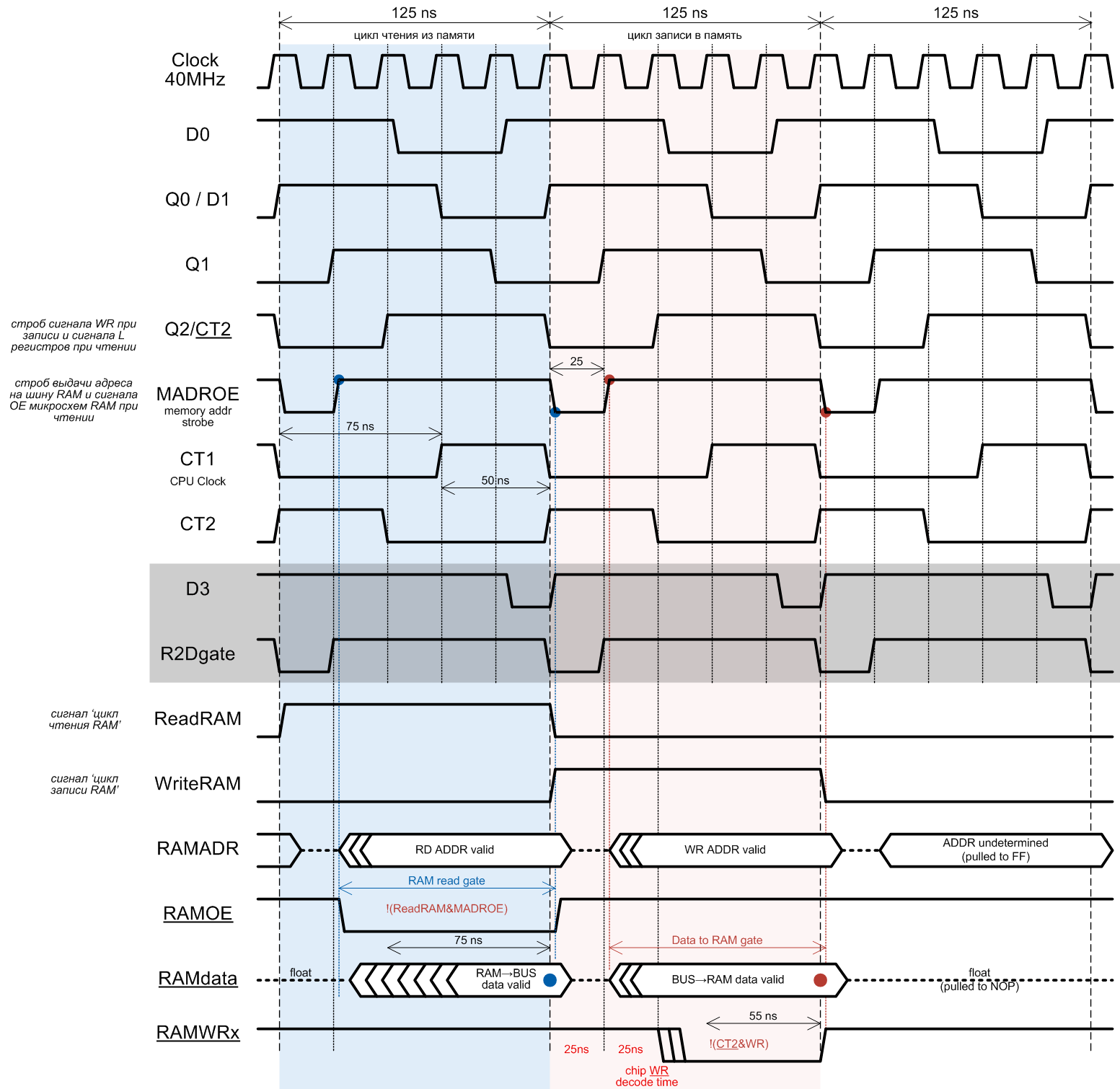

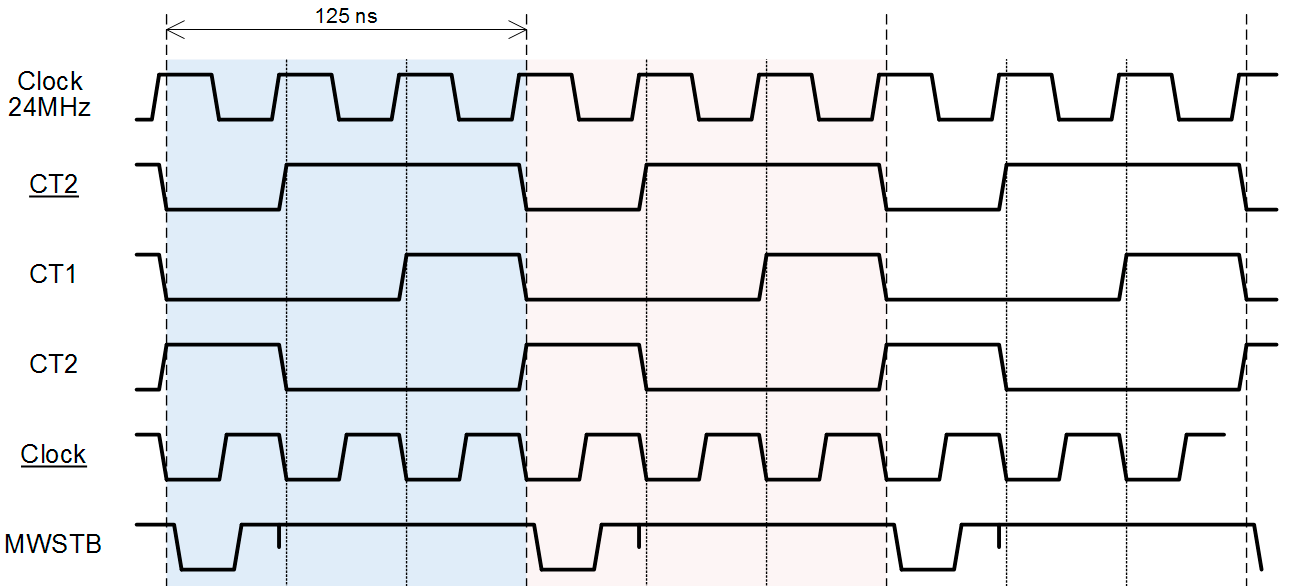

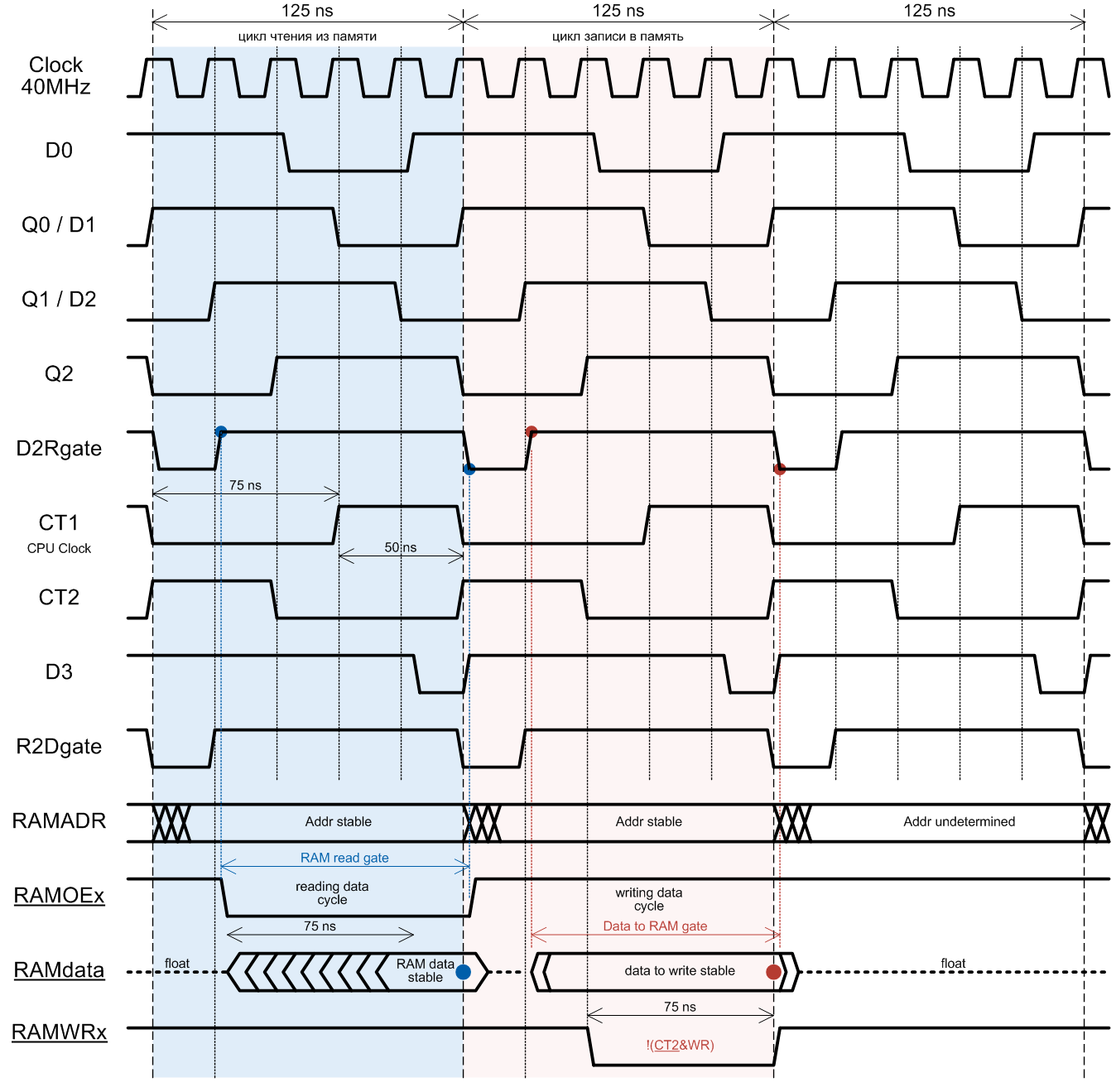

И самое главное - диаграмма работы

Тут самое интересное.

CT1 - это такт процессора. Процессору данные нужны по спаду такта. Посему такая логическая разбивка времени.

ReadRAM и WriteRAM - это сигналы, формируемые диспетчером доступа, означают, что происходит с памятью.

RamOE - подаётся на чипы памяти для включения их выхода, активируется только в цикле чтения.

В цикле записи активируется другой сигнал RegOE, формируемый на основе MADROE - включает выходы регистров данных с байтами для записи в память.

По окончании цикла все сигналы с шины памяти снимаются на 20-25 нс, до фронта сигнала MADROE (MASTB) - это обеспечивает гарантию отсутствия перекрытия циклов. Оставшееся время порядка 100 нс вполне достаточно для нормальной работы памяти.

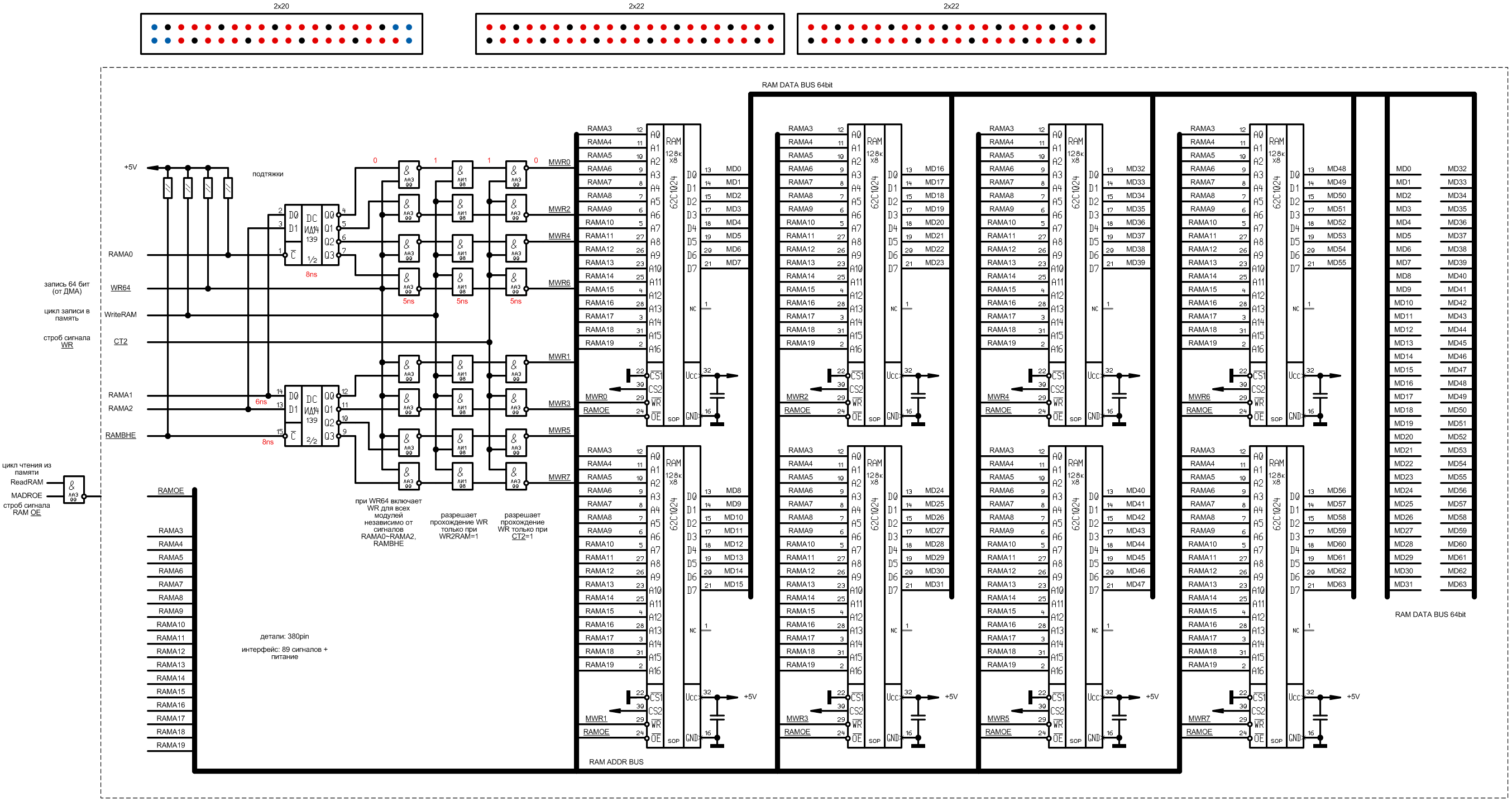

Сам модуль памяти планируется 64-разрядным. Это накладывает некоторые особенности

Процессору 64 разряда не нужны, но нужны для видеоадаптера, чтобы за раз он мог забирать данные для 256-цветных 8 пикселей, иначе ему придётся обращаться к памяти намного чаще.

Слегка чуждый для памяти сигнал CT2 всё-же необходим. С его помощью формируется сигнал WR, который должен подниматься никак не позже окончания цикла и съёма данных и адреса. Данная схема это гарантирует, хотя есть скользкое место, заключающееся в том, что скорость работы ИД14 не бесконечно большая и есть опасения, что могут быть ложные "пички" уже после прихода CT. Хотя в принципе, порядка 15-20 нс на дешифрацию есть.

Как выход из ситуации можно предложить замеc сигнала CT2 с сигналами RAMA0 и BHE - это гарантирует отсутствие "пичек" при любых обстроятельствах, но скорее всего задержит WR. Возможно, что это не критично т.к. по даташиту длительность WR должна быть не менее 50нс, что даёт достаточно времени.

Такой сложный декодер для WR нужен потому что процессор может писать как байтами, так и словами, а память в сумме 64 бита. Поэтому надо выбрать конкретные чипы для записи, а не во все подряд.

А вот чтение с этого модуля всегда происходит на всю ширину. Для процессора далее из 8 регистров, предназначенных для гейта данных RAM-CPU, будут выбраны один или два, с которых чтение и произойдёт. Видеоадаптер же всегда читает 64 бита. DMA - пока вопрос открытый, но по умолчанию работает аналогично процессору, однако задел на 64 бита сделан в виде вывода WR64 - при его активации сигнал записи активируется на всех чипах, независимо от BHE, RAMA0~RAMA2

Память наверное лучше оформить отдельным модулем. Там где-то в районе 400 пинов.

Делитель на 3 можно сделать на D-триггерах (flip-flop) ТМ2. Сигналы получаются такие же.

Здесь нижняя ТМ2 уже относится к селектору, его посмотрим позже. Остальные сигналы такие же. Но не полностью показа формирователь стробов.

У делителей на 3 плохо то, что второй полупериод таковой процессора не получается сделать 50 нс, получается только 41. Понятия не имею, может ли это привести к проблемам. Возможно, нет. Однако унифицирование диаграмм позволит попробовать оба варианта генераторов.

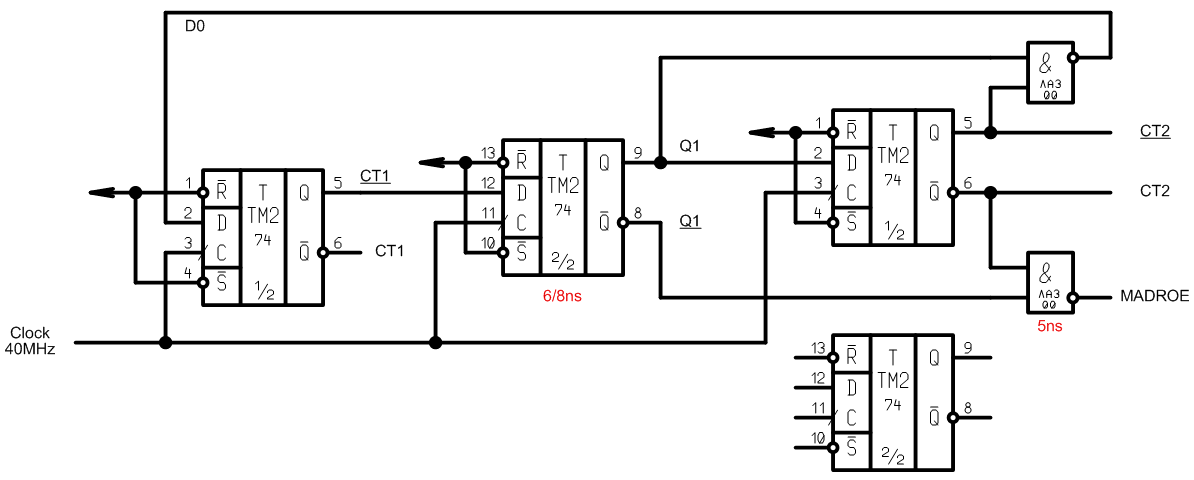

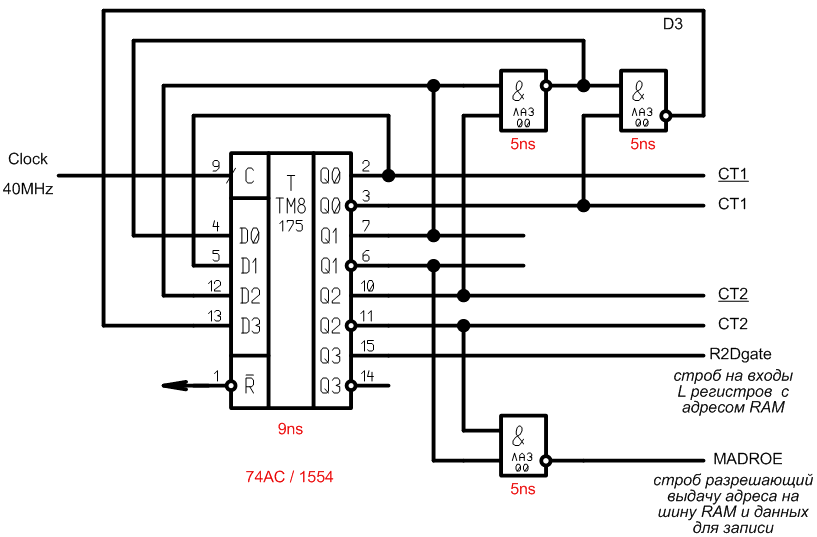

Делитель на 5 даёт точные временнЫе соотношения 75 и 50нс (без учёта фронтов). Его можно сделать на трёх D-триггерах (ТМ2 или ТМ8). Один свободный триггер можно использовать для чего-нибудь ещё, ну или просто для разветвления сигнала, например CT2 - он много где потребуется.

Сигналы те же. Из-за чуть другого количества фронтов временнЫе характеристики слегка другие, но это не принципиально.

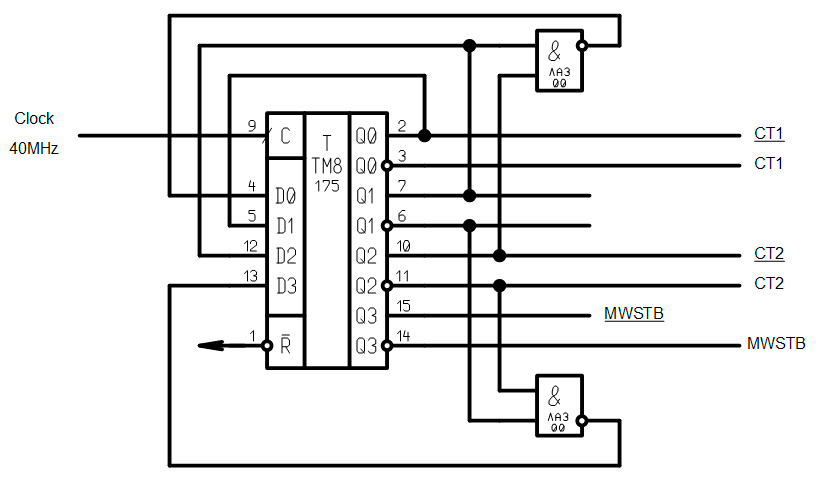

То же на ТМ8

На ТМ8 четвёртым триггером можно сформировать сигнал, аналогичный MADROE, но идущий на несколько нс раньше. К сожалению, сделать так, чтобы он начинался чуть ранее MADROE, а заканчивался так же, у меня не получается. Как уже говорил, наверное MADROE будет достаточно, но пока не сделаешь в железе - не узнаешь.

Диаграммы выглядят так

Полагаю, на такой вид диаграмм работы с памятью и рассчитывать в дальнейшем.

Да, про BHE - Byte High Enable. Немного недоумеваю, почему ADR0 не называется BLE - Byte Low Enable. Ну да ладно.

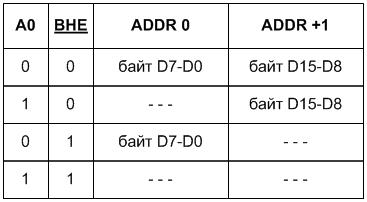

Суть в том, что эти два сигнала ADR0 и BHE индицируют, с какими линиями данных сейчас работает процессор. Лучше всего это отображает табличка

При этом A0, как и BHE как бы не являются адресными сигналами памяти, а только указывают на конкретные байты (младший и/или старший) в слове. Но скорее всего название A0 оставлено для логической совместимости с 8-разрядной адресацией.

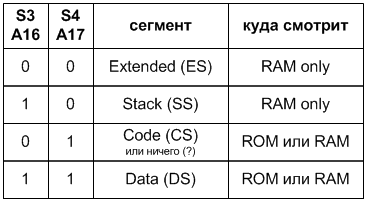

Да, даже в Minimum Mode процессор при обращении с данными указывает, какому сегменту (CS, DS, ES, SS) они принадлежат. После сигнала ALE, защёлкивающего адрес в регистрах, на шину поставляются сигналы S3 и S4, указывающие на конкретный сегмент. Если их использовать, то появляется возможность хоть для каждого сегмента выделить свой собственный мегабайт памяти, что в сумме составит 4 мегабайта максивально возможной памяти, с которой может работать процессор, но на деле такое разбиение неудобно. Однако, если учесть то, что в адресном пространстве всегда есть ПЗУ и видеопамять, мне видится интересным сделать такое разбиение: сегменты CS и DS всегда обращаются к области ПЗУ, где оно перекрывает ОЗУ. А сегменты ES и SS всегда обращаются только к ОЗУ. Это позволит использовать перекрытую ПЗУ память для данных и стека.

Вот табличка

Интресно, ПЗУ сколько по объём надо? 64кБ поди хватит... Накидаем схемку выборки ПЗУ, она будет странная, если не хотим использовать 16-битное ПЗУ (такие тоже есть, ну или две микросхемы можно поставить, но это мне не нравится, одна лучше даже с точки зрения программирования).

Первый - делитель на три на основе JK-триггеров

Сигнал MASTB вспомогательный, по его восходящему фронту и до конца цикла формируется сигнал MADROE (Memory ADdR Output Enable) - строб, подаваемый на регистры, содержащие адрес, подаваемый на шину RAM

Очень примерно это может выглядеть так (схема без подробностей, только для понимания)

И самое главное - диаграмма работы

Тут самое интересное.

CT1 - это такт процессора. Процессору данные нужны по спаду такта. Посему такая логическая разбивка времени.

ReadRAM и WriteRAM - это сигналы, формируемые диспетчером доступа, означают, что происходит с памятью.

RamOE - подаётся на чипы памяти для включения их выхода, активируется только в цикле чтения.

В цикле записи активируется другой сигнал RegOE, формируемый на основе MADROE - включает выходы регистров данных с байтами для записи в память.

По окончании цикла все сигналы с шины памяти снимаются на 20-25 нс, до фронта сигнала MADROE (MASTB) - это обеспечивает гарантию отсутствия перекрытия циклов. Оставшееся время порядка 100 нс вполне достаточно для нормальной работы памяти.

Сам модуль памяти планируется 64-разрядным. Это накладывает некоторые особенности

Процессору 64 разряда не нужны, но нужны для видеоадаптера, чтобы за раз он мог забирать данные для 256-цветных 8 пикселей, иначе ему придётся обращаться к памяти намного чаще.

Слегка чуждый для памяти сигнал CT2 всё-же необходим. С его помощью формируется сигнал WR, который должен подниматься никак не позже окончания цикла и съёма данных и адреса. Данная схема это гарантирует, хотя есть скользкое место, заключающееся в том, что скорость работы ИД14 не бесконечно большая и есть опасения, что могут быть ложные "пички" уже после прихода CT. Хотя в принципе, порядка 15-20 нс на дешифрацию есть.

Как выход из ситуации можно предложить замеc сигнала CT2 с сигналами RAMA0 и BHE - это гарантирует отсутствие "пичек" при любых обстроятельствах, но скорее всего задержит WR. Возможно, что это не критично т.к. по даташиту длительность WR должна быть не менее 50нс, что даёт достаточно времени.

Такой сложный декодер для WR нужен потому что процессор может писать как байтами, так и словами, а память в сумме 64 бита. Поэтому надо выбрать конкретные чипы для записи, а не во все подряд.

А вот чтение с этого модуля всегда происходит на всю ширину. Для процессора далее из 8 регистров, предназначенных для гейта данных RAM-CPU, будут выбраны один или два, с которых чтение и произойдёт. Видеоадаптер же всегда читает 64 бита. DMA - пока вопрос открытый, но по умолчанию работает аналогично процессору, однако задел на 64 бита сделан в виде вывода WR64 - при его активации сигнал записи активируется на всех чипах, независимо от BHE, RAMA0~RAMA2

Память наверное лучше оформить отдельным модулем. Там где-то в районе 400 пинов.

Делитель на 3 можно сделать на D-триггерах (flip-flop) ТМ2. Сигналы получаются такие же.

Здесь нижняя ТМ2 уже относится к селектору, его посмотрим позже. Остальные сигналы такие же. Но не полностью показа формирователь стробов.

У делителей на 3 плохо то, что второй полупериод таковой процессора не получается сделать 50 нс, получается только 41. Понятия не имею, может ли это привести к проблемам. Возможно, нет. Однако унифицирование диаграмм позволит попробовать оба варианта генераторов.

Делитель на 5 даёт точные временнЫе соотношения 75 и 50нс (без учёта фронтов). Его можно сделать на трёх D-триггерах (ТМ2 или ТМ8). Один свободный триггер можно использовать для чего-нибудь ещё, ну или просто для разветвления сигнала, например CT2 - он много где потребуется.

Сигналы те же. Из-за чуть другого количества фронтов временнЫе характеристики слегка другие, но это не принципиально.

То же на ТМ8

На ТМ8 четвёртым триггером можно сформировать сигнал, аналогичный MADROE, но идущий на несколько нс раньше. К сожалению, сделать так, чтобы он начинался чуть ранее MADROE, а заканчивался так же, у меня не получается. Как уже говорил, наверное MADROE будет достаточно, но пока не сделаешь в железе - не узнаешь.

Диаграммы выглядят так

Полагаю, на такой вид диаграмм работы с памятью и рассчитывать в дальнейшем.

Да, про BHE - Byte High Enable. Немного недоумеваю, почему ADR0 не называется BLE - Byte Low Enable. Ну да ладно.

Суть в том, что эти два сигнала ADR0 и BHE индицируют, с какими линиями данных сейчас работает процессор. Лучше всего это отображает табличка

При этом A0, как и BHE как бы не являются адресными сигналами памяти, а только указывают на конкретные байты (младший и/или старший) в слове. Но скорее всего название A0 оставлено для логической совместимости с 8-разрядной адресацией.

Да, даже в Minimum Mode процессор при обращении с данными указывает, какому сегменту (CS, DS, ES, SS) они принадлежат. После сигнала ALE, защёлкивающего адрес в регистрах, на шину поставляются сигналы S3 и S4, указывающие на конкретный сегмент. Если их использовать, то появляется возможность хоть для каждого сегмента выделить свой собственный мегабайт памяти, что в сумме составит 4 мегабайта максивально возможной памяти, с которой может работать процессор, но на деле такое разбиение неудобно. Однако, если учесть то, что в адресном пространстве всегда есть ПЗУ и видеопамять, мне видится интересным сделать такое разбиение: сегменты CS и DS всегда обращаются к области ПЗУ, где оно перекрывает ОЗУ. А сегменты ES и SS всегда обращаются только к ОЗУ. Это позволит использовать перекрытую ПЗУ память для данных и стека.

Вот табличка

Интресно, ПЗУ сколько по объём надо? 64кБ поди хватит... Накидаем схемку выборки ПЗУ, она будет странная, если не хотим использовать 16-битное ПЗУ (такие тоже есть, ну или две микросхемы можно поставить, но это мне не нравится, одна лучше даже с точки зрения программирования).

#2

Цифровая техника / Re: Запустить 8086

Последний ответ от Slabovik - 06 Май, 2024, 13:34Что-то трудно с этим генератором. Не, на 3 делит чётко. Но задержками играть получается только на TTL сериях, у которых переход от 1 к 0 и от 0 к 1 происходит за разное время. У серии 74AC разница весьма незначительна, поэтому растянуть второй полупериод так просто не получается.

Слегка изменил положение строба шины

Но по всему выходит и формирование строба чуток кривое - возможен глитч и без дополнительного обвеса его не побороть, и второй полупериод такта процессора коротковат от даташита.

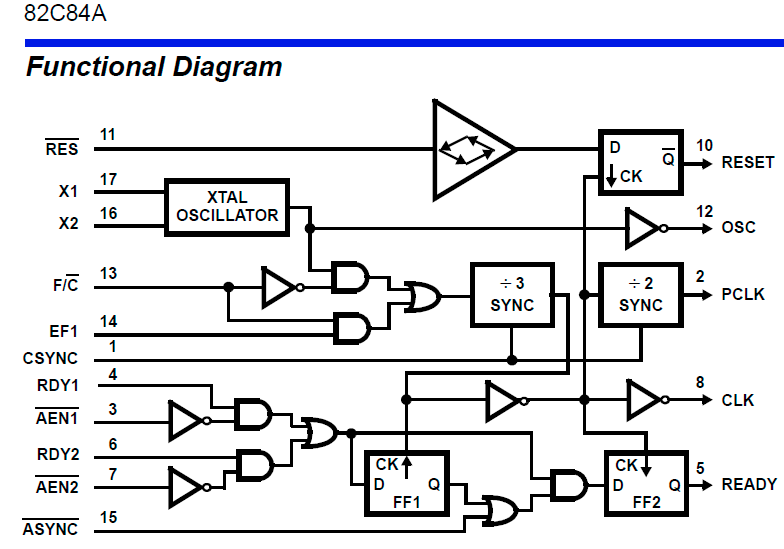

Но с другой стороны я смотрю даташит на его родной геренатор. Там делитель на 3, вот в чём прикол!

Слегка изменил положение строба шины

Но по всему выходит и формирование строба чуток кривое - возможен глитч и без дополнительного обвеса его не побороть, и второй полупериод такта процессора коротковат от даташита.

Но с другой стороны я смотрю даташит на его родной геренатор. Там делитель на 3, вот в чём прикол!

ЦитатаThe CLK output is a 33% duty cycle clock driver designed toИ, как такое бывает?

drive the 80C86, 80C88 processors directly.

#3

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от Slabovik - 06 Май, 2024, 11:39Смотрю, озадачил я тебя  Но увы, такова цена многозадачности. Мы ещё реентерабельность ни разу не рассматривали

Но увы, такова цена многозадачности. Мы ещё реентерабельность ни разу не рассматривали  Впрочем, здесь она не нужна, я полагаю...

Впрочем, здесь она не нужна, я полагаю...

Но увы, такова цена многозадачности. Мы ещё реентерабельность ни разу не рассматривали

Но увы, такова цена многозадачности. Мы ещё реентерабельность ни разу не рассматривали  Впрочем, здесь она не нужна, я полагаю...

Впрочем, здесь она не нужна, я полагаю... #4

Цифровая техника / Re: Запустить 8086

Последний ответ от Slabovik - 04 Май, 2024, 18:12Продолжим. 40МГц тактирования позволяет удобно определить цикл шины памяти с 25-наносекундным дедтаймом. Он нужен изза того, что память не очень быстро снимает данные со своего выхода после цикла чтения, и если следующим будет идти цикл записи, там целых полтора-два десятка наносекунд может быть игра "перетяни шину". Чтобы этого не было, данные нужно выставлять слегка позже, чем начинается цикл.

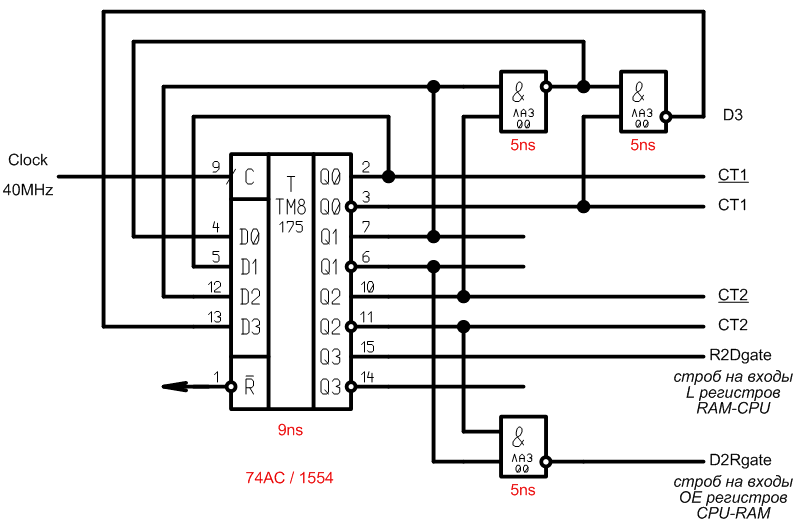

Слегка изменил схему генератора

По-идее, можно обойтись без четвёртого (D3/Q3) триггера, но его девать некуда - пусть стробирует гейт на выводы 'L' триггеров ИР22, которые забирают данные из памяти.

Строб гейтов данных на запись в память выглядит точно также, только следует чуть позже за счёт задержки в логическом элементе.

Постарался наиболее точно отобразить задержки в элементах. В основу взял серию 74AC

Можно частоту делить на 3, взяв в качестве опорной 24МГц. Это проще. Но поделив на D-триггерах, получим ровно 1/3, получим 41нс полутакта, а по документам надо 50.

Можно попробовать посчитать делитель на 3 на JK-триггерах. Это асинхронные триггеры и фронты будут за счёт задержек смещены, возможно, в нужную сторону. Посмотрим. Вот схема делителя

Пойду тайминги рисовать

Слегка изменил схему генератора

По-идее, можно обойтись без четвёртого (D3/Q3) триггера, но его девать некуда - пусть стробирует гейт на выводы 'L' триггеров ИР22, которые забирают данные из памяти.

Строб гейтов данных на запись в память выглядит точно также, только следует чуть позже за счёт задержки в логическом элементе.

Постарался наиболее точно отобразить задержки в элементах. В основу взял серию 74AC

Можно частоту делить на 3, взяв в качестве опорной 24МГц. Это проще. Но поделив на D-триггерах, получим ровно 1/3, получим 41нс полутакта, а по документам надо 50.

Можно попробовать посчитать делитель на 3 на JK-триггерах. Это асинхронные триггеры и фронты будут за счёт задержек смещены, возможно, в нужную сторону. Посмотрим. Вот схема делителя

Пойду тайминги рисовать

#5

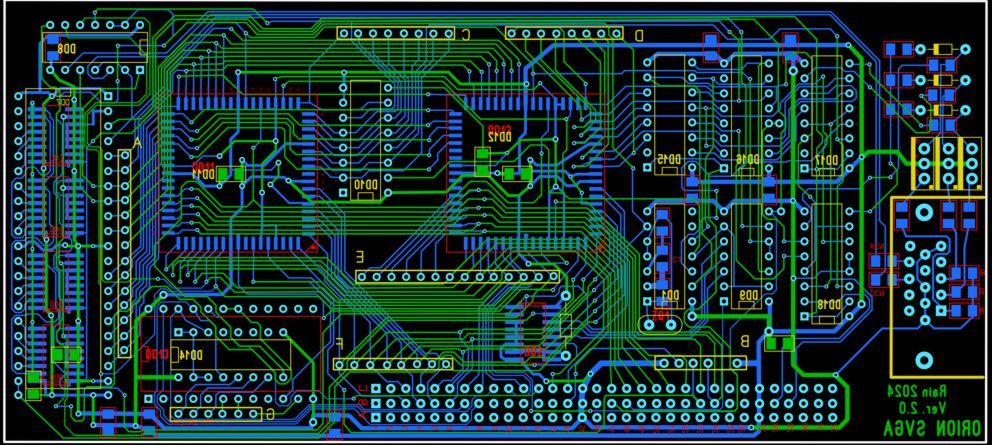

Цифровая техника / Re: Re: Орион-128 возрождение ...

Последний ответ от matrixplus - 04 Май, 2024, 13:15запись на проект плат SVGA https://zx-pk.com/forum/viewtopic.php?f=7&t=23750

Орион-128 плата SVGA проект (улучшение изображения) http://rdk.regionsv.ru/orion128-super-42-turbo.htm

Принимаются заявки: цена приблизительно озвучена на https://zx-pk.com/forum/viewtopic.php?f=7&t=23750

информация http://rdk.regionsv.ru/orion128-super-42-turbo.htm

фото платы http://rdk.regionsv.ru/orion128svga/svga-015.jpg

в ней предусмотрены раьемы для платки расширения которая уже есть (в принципе разведена но ее бум делать позже)

Орион-128 плата SVGA проект (улучшение изображения) http://rdk.regionsv.ru/orion128-super-42-turbo.htm

Принимаются заявки: цена приблизительно озвучена на https://zx-pk.com/forum/viewtopic.php?f=7&t=23750

информация http://rdk.regionsv.ru/orion128-super-42-turbo.htm

фото платы http://rdk.regionsv.ru/orion128svga/svga-015.jpg

в ней предусмотрены раьемы для платки расширения которая уже есть (в принципе разведена но ее бум делать позже)

#6

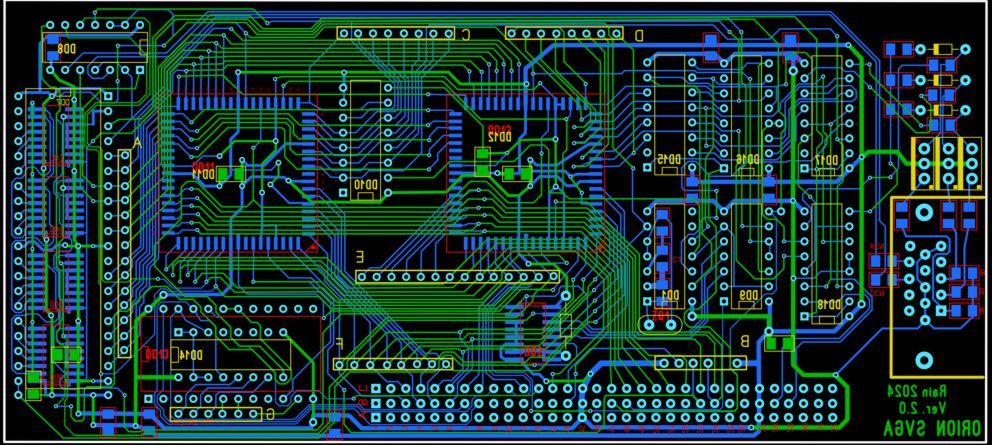

Фото, видео, аудио / Re: Коротко о погоде

Последний ответ от Slabovik - 03 Май, 2024, 22:13Целый день пасмурно и прохладно, что даже до +4 еле-еле прогрело. Но с обеда зарядил дождь, который к вечеру превратился в мокрый снег, а потом в сильный мокрый снег. Ладно, что деревья ещё сильно лист не выпустили, даже вишни со сливами бутоны только-только приготовили, но тополя в городе поломало конечно... Полагаю, обойдётся

#7

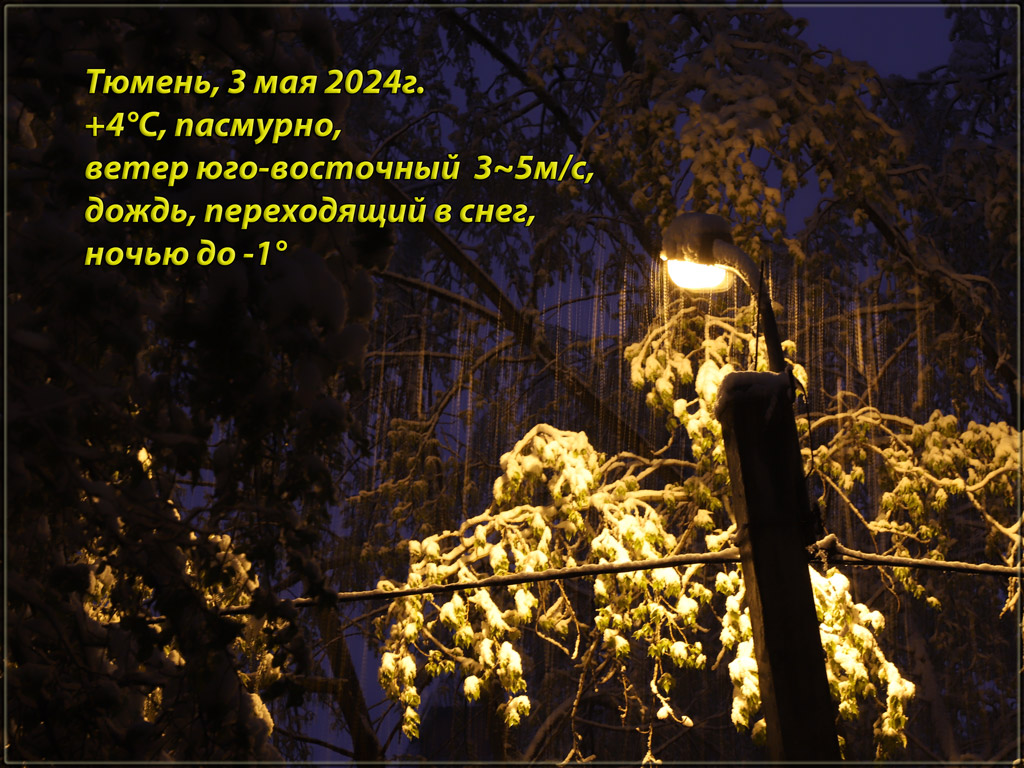

Цифровая техника / Запустить 8086

Последний ответ от Slabovik - 03 Май, 2024, 16:43Давно колупаюсь, когда время есть, но до практики так и не добрался ввиду объёмных затрат на хардварь. Тем не менее, давно хотел сделать какой-нибудь контроллер на базе этого проца. Да, есть NEC V40, но это уже перебор

Итак, имеем i8086 либо подобный. Задача-минимум - запустить. Задача-максимум - с прозрачным режимом работы с памятью и собственным видеоконтроллером, дающим картинку на телевизор либо LCD. 256 цветов достаточно. 16 - минималка.

8086 есть в нескольких вариантах. 8086 - базовый с тактовой 5МГц. 8086-2 имеет тактовую 8МГц. И есть редкий 8086-1 с тактовой 10МГц. Базовый купить полный кулёк не проблема, их много продают с разборок. 8086-2 надо поискать. 10-мегагерцовый вариант я не находил. А есть ещё вариант 80С86 - то же самое, только по КМОП-технологии.

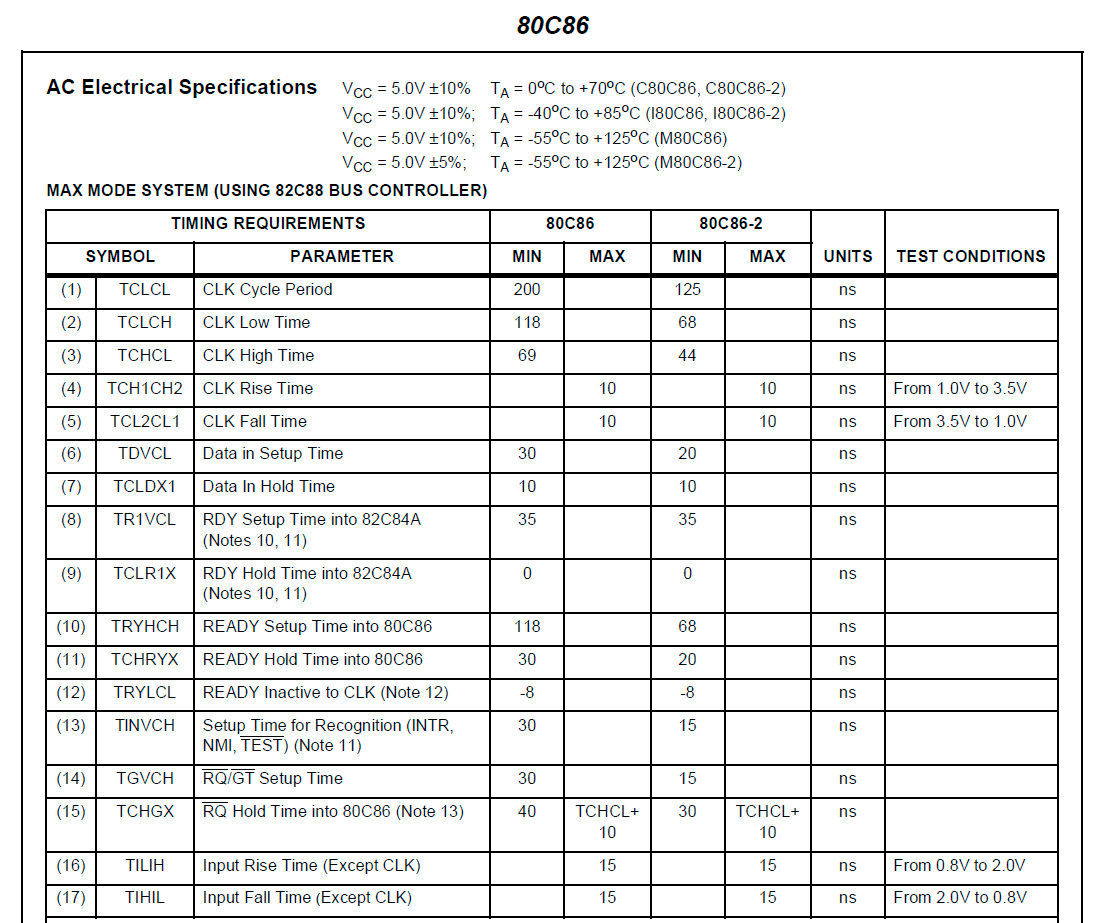

Для начала надо разобраться с тактированием. Оно по-интеловски слегка странное - соотношение полупериодов должно быть 3/5 и 2/5

Тайминги версии 80C86 идентичны таймингам оригинала

Да, я видел варианты, где делают 2/3 и 1/3 и даже 3/4 и 1/4, но это с пониженными частотами, 4 а не 5, 6 а не 8...

Для 8-мегагерцового 1/3 при 125нс периоде получается только 41нс, а не 50, требуемых по даташиту (45+фронт)

3/5 и 2/5 можно чётко получить при 40-мегагерцовом осцилляторе

Здесь подаваемая на процессор частота CT1, другие сигналы полезные для синхронизации узлов.

уфф, оказалось, у меня потерялась циклограмма. Потребуется время нарисовать по-новой... продолжу...

Итак, имеем i8086 либо подобный. Задача-минимум - запустить. Задача-максимум - с прозрачным режимом работы с памятью и собственным видеоконтроллером, дающим картинку на телевизор либо LCD. 256 цветов достаточно. 16 - минималка.

8086 есть в нескольких вариантах. 8086 - базовый с тактовой 5МГц. 8086-2 имеет тактовую 8МГц. И есть редкий 8086-1 с тактовой 10МГц. Базовый купить полный кулёк не проблема, их много продают с разборок. 8086-2 надо поискать. 10-мегагерцовый вариант я не находил. А есть ещё вариант 80С86 - то же самое, только по КМОП-технологии.

Для начала надо разобраться с тактированием. Оно по-интеловски слегка странное - соотношение полупериодов должно быть 3/5 и 2/5

Тайминги версии 80C86 идентичны таймингам оригинала

Да, я видел варианты, где делают 2/3 и 1/3 и даже 3/4 и 1/4, но это с пониженными частотами, 4 а не 5, 6 а не 8...

Для 8-мегагерцового 1/3 при 125нс периоде получается только 41нс, а не 50, требуемых по даташиту (45+фронт)

3/5 и 2/5 можно чётко получить при 40-мегагерцовом осцилляторе

Здесь подаваемая на процессор частота CT1, другие сигналы полезные для синхронизации узлов.

уфф, оказалось, у меня потерялась циклограмма. Потребуется время нарисовать по-новой... продолжу...

#8

Путешествия / Re: Из кабины машиниста

Последний ответ от Slabovik - 03 Май, 2024, 13:37Снег идёт и поезд идёт. Зимняя Швейцария

St.Moritz - Chur with heavy snowfall

[свернуть]

#9

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от zenon - 02 Май, 2024, 21:53Случайно удалил свой пост.

Предделитель для 1Гц будет такой:

72000000/7200 = 10000Гц

Предзагрузка 10000.

Прерывание по переполнению счётчика:

Но, у нас ещё есть собственное прерывание на SPI: void SPI1_IRQHandler()

Предделитель для 1Гц будет такой:

72000000/7200 = 10000Гц

Предзагрузка 10000.

Прерывание по переполнению счётчика:

↓ спойлер ↓

void TIM13_init(void){

RCC->APB1ENR |= RCC_APB1ENR_TIM3EN; // разрешить тактирование таймера

TIM3->PSC = 7200 - 1; // предделитель

TIM3->ARR = 10000 - 1; // предзагрузка

TIM3->DIER |= TIM_DIER_UIE; // прерывания будем ловить по переполнению счетчика

TIM3->CR1 |= TIM_CR1_CEN;

NVIC_EnableIRQ(TIM3_IRQn);

}

void TIM3_IRQHandler (void) {

if ((TIM3->SR & TIM_SR_UIF) == TIM_SR_UIF) { // проверяем, что прерывание произошло по событию переполнения счетчика stm32f10x.h

TIM3->SR &= ~TIM_SR_UIF; // флаг сбросить, иначе при выходе из обработчика прерываний мы тут же попадем туда снова

LEDTOGGLE; // моргаем

}

}[свернуть]

Но, у нас ещё есть собственное прерывание на SPI: void SPI1_IRQHandler()

#10

Цифровая техника / Re: Светодиодные матрицы

Последний ответ от Slabovik - 02 Май, 2024, 19:14Это немного другая организация процесса, но в принципе подходит. Основной цикл крутит круги, в которых вызываются все процедуры. А процедуры уже смотрят, пора им или ещё нет. Тут проблема может быть в том, что вдруг возможен какой-то длительный процесс/процедура, а эта штука его прерывать не сможет. Прерывания помогают отделить процессы друг от друга.