# MODERN DC-TO-DC **SWITCHMODE POWER** CONVERTER **CIRCUITS**

Rudolf P. Severns Gordon E. Bloom

| ,      |

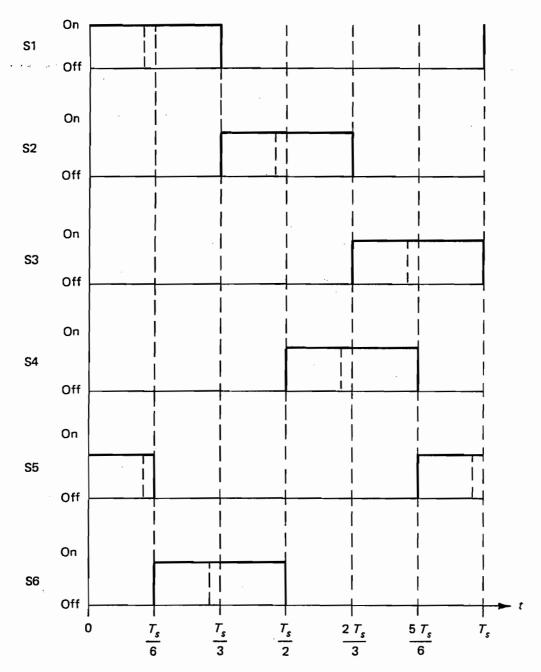

|--------|

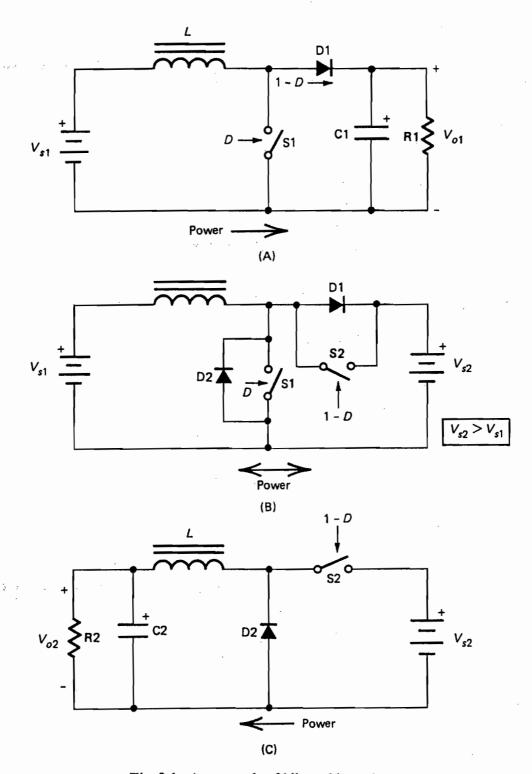

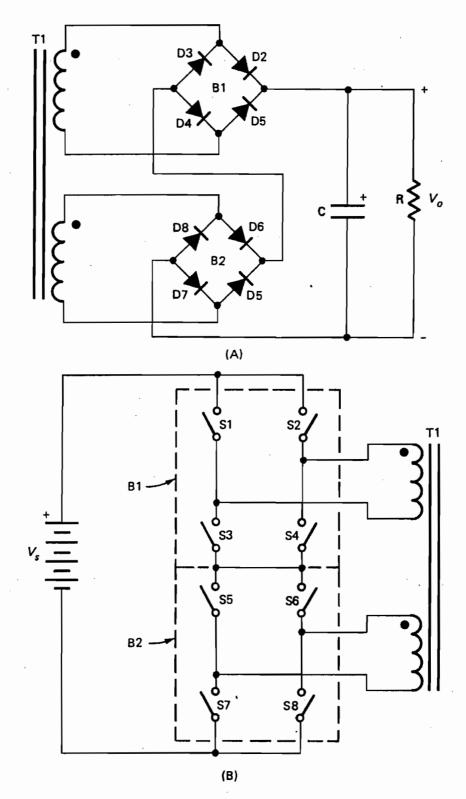

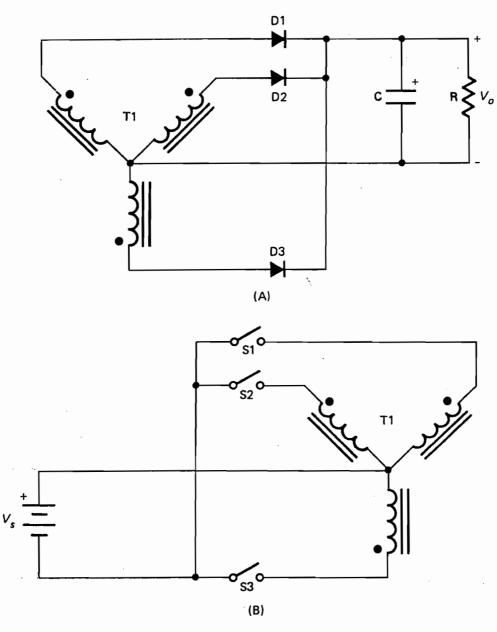

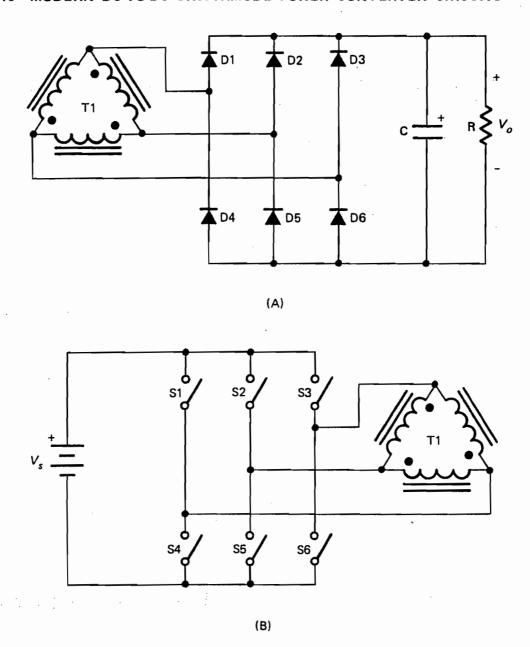

|        |

|        |

|        |

| 1. 14. |

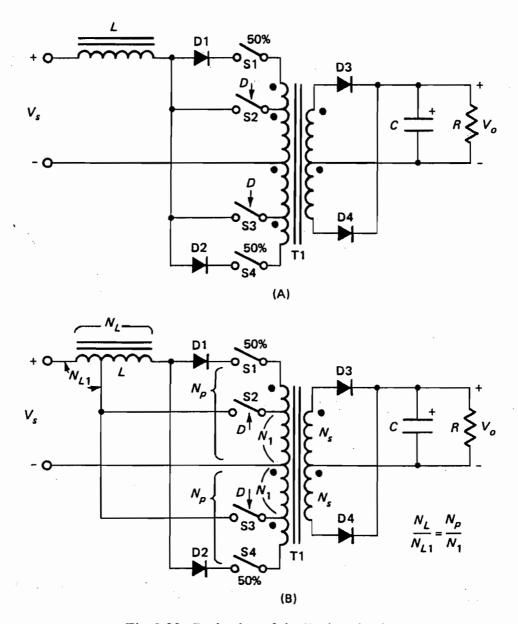

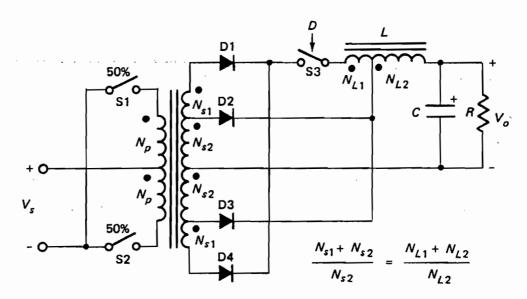

|        |

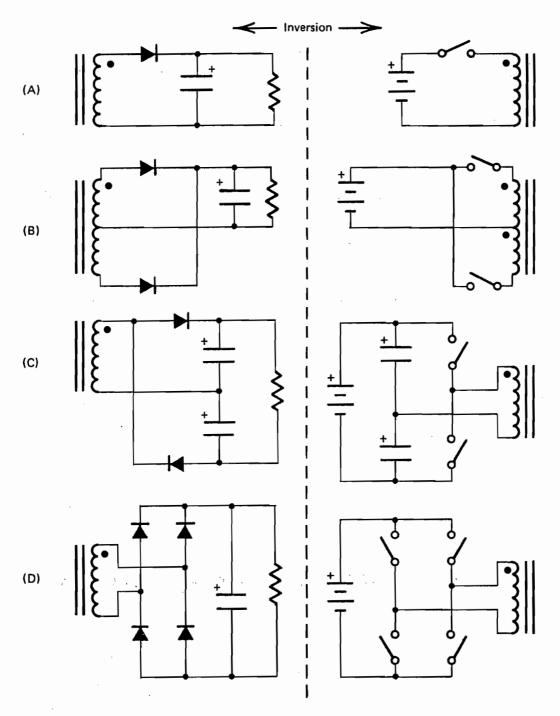

| ٠,     |

|        |

| _      |

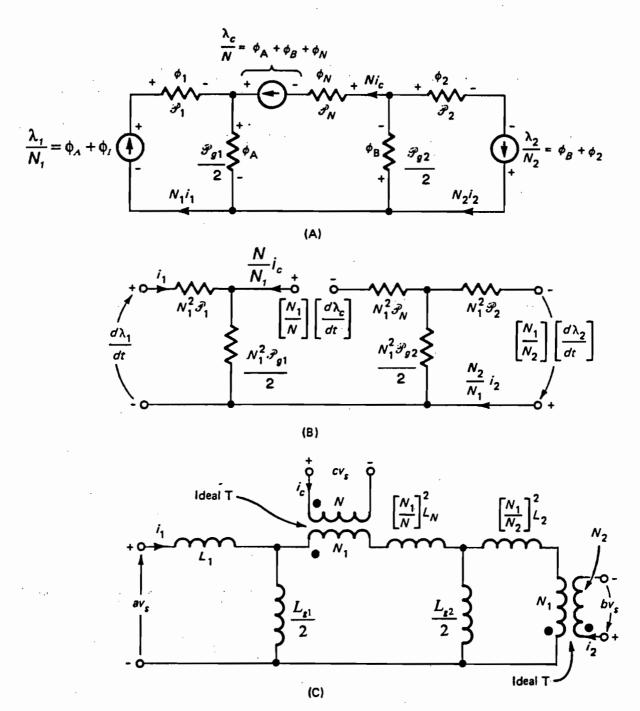

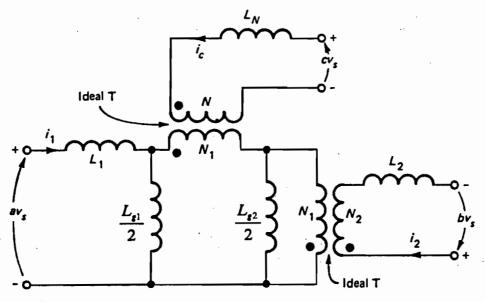

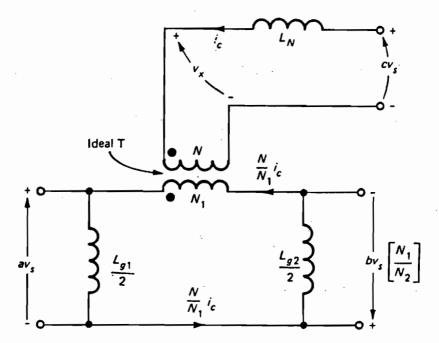

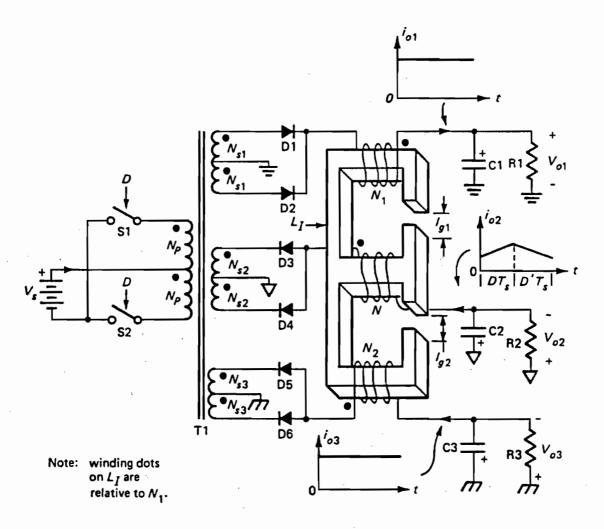

|        |

|        |

| `      |

|        |

| <      |

|        |

| . 4    |

|        |

|        |

| 1.5    |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

| *,     |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

| *      |

| ,      |

| ,      |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

# MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

Rudolf P. Severns

President Springtime Enterprises, Inc.

Gordon (Ed) Bloom

President e/j BLOOM associates, Inc.

specialists in practical design seminars for

power electronics engineers

115 Duran Drive San Rafael, CA 94903 (415) 492-8443 (415) 492-1239 FAX

#### Copyright © 1985 by Rudolf P. Severns and Gordon Bloom

Library of Congress Catalog Card Number 84-12026 ISBN 0-442-21396-4

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means - graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems - without written permission of the publisher.

Printed in the United States of America

Reprinted by e/j BLOOM associates Inc. Educational Division 115 Duran Drive San Rafael, California U.S.A. 94903 Telephone: (415) 492-8443

FAX:

(415) 492-1239

Library of Congress Cataloging in Publication Data

Severns, Rudolf P. Modern DC-to-DC switchmode power converter circuits.

Bibliography: p. Includes index.

- 1. Electronic apparatus and appliances-Power supply.

- 2. Microelectronics Power supply.

- I. Bloom, Gordon.

- II. Title.

- III. Title: Modern DC-to-DC switchmode Power converter circuits.

- IV. Series.

TK7868.P6S47 1984

621.3815'32

84-12026

ISBN 0-442-21396-4

FOR

JOY AND DIANA

AND

THE UNSUNG HERO

OF

ELECTRONIC DESIGN,

THE POWER SUPPLY ENGINEER

#### About the Authors

Rudolf P. Severns is the President of Springtime Enterprises, Inc., a power converter design consulting firm. His 33 years of experience in power converter design include work with TRW, Lockheed, Hughes Aircraft, Magnavox, and the University of California. In 1978 Mr. Severns gave the first public demonstration of power converters operating with switching frequencies above 100 kHz. A year later he presented the first unified view of switchmode power converter circuits that related the many different circuits, and showed that many new and useful circuits could be created. He has also played a leading role in developing an understanding of power MOSFET operation and how to properly use these devices in power converters. Mr. Severns received his BS in engineering from the University of California at Los Angeles.

Gordon (Ed) Bloom is the President of e/j BLOOM associates, Inc., a consulting firm devoted to the organization and sponsorship of power electronics short courses for electronic engineers throughout the United States and Canada. An experienced designer, manager and analyst in the field of power conversion design, he is now a consultant to major industrial firms in power supply design and development. Prior to beginning his own company, he held key designer positions with subdivisions of Litton Industries, General Dynamics, Teledyne, Honeywell, and EG&G. Over his 30 years of work experiences, he has written numerous articles and technical papers on the subjects of power converter and regulator design, and holds seven U.S. patents on unique power converter topologies. He is a Senior Member of the Institute of Electrical and Electronic Engineers and holds a Master's Degree in Electrical Engineering from San Diego State College. He is one of the few engineers in the world today presently engaged in active research in practical magnetic integration techniques for switchmode power converters, and was the first person to systematically demonstrate the universal application of these techniques in all DC-to-DC converter circuits.

#### MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS Rudolf P. Severns and Gordon (Ed) Bloom

Significant advances in the micro-miniaturization of electronic systems have spurred the creation of space-saving switchmode conversion techniques for the design of highly efficient power processing equipment. Yet while there are literally hundreds of switchmode power converter (SPCs) circuit variations, the vast majority of today's electronic design engineers have not tapped their vast potential. This is largely because practical, up-to-date information on the design of SPCs has been scattered throughout numerous publications, technical papers, and other scientific reporting media.

Severns and Bloom's Modern DC-to-DC Switchmode Power Converter Circuits now makes that valuable information available for the first time in one unified volume. The book focuses on the fundamental behavior and characteristics of SPCs and on the relative merits of many SPC circuit topologies. Chapters 1 through 11 present the basic theory of SPC circuits, with minimal use of mathematics. The book begins by exploring the signal characteristics of two elementary SPC circuits and then builds progressively to more complex circuits by using combinations of the basic circuits in conjunction with synthesis techniques. Chapter 12 then offers detailed discussion of converters whose primary inductive and transformer elements have been integrated into single physical assemblies. In many cases, the designs shown here, and the methods behind this magnetic integration process, have never appeared before in any other publication. The book concludes with an extensive bibliography and helpful lists of suggested reading materials that can be used for reference and research purposes.

A powerful working tool for both the inexperienced and veteran designer of SPC circuits, Modern DC-to-DC Switchmode Power Converter Circuits represents a major step toward finally unleashing the extraordinary capabilities of SPC circuit variations.

## **Foreword**

As each area of technology with a potential for significantly impacting any major segment of the electronics industry evolves, it often is accompanied by the development of a succession of new circuits. Each new circuit indeed appears different, employing different components in differing configurations, and claims an assortment of distinct features of "improved performance." Without a considerable investment of laboratory time to construct, evaluate, and compare each candidate circuit, it usually is difficult to realistically appraise the relative merits of one approach over another. It often is even more difficult to identify the underlying principles which point up basic similarities and differences. Such is the situation in the new and rapidly expanding area known as electronic power processing or switching mode power supplies.

The area of switching power supplies has been spurred by the need for power sources of higher performance, smaller volume, and lighter weight in order to achieve compatibility with the shrinking size of all forms of communication and data handling systems, and particularly with the portable battery-operated equipment in everything from home appliances and handtools to mobile communication equipment. Static dc-to-dc converters and dc-to-ac inverters provide a natural interface with the new direct energy sources such as solar cells, fuel cells, thermoelectric generators, and the like, and form the central ingredient in most uninterruptable power sources. Such solid-state power conditioners operating with internal conversion frequencies of tens to hundreds of kilohertz are emerging as the new mainstay of most power supplies for computers and communication systems, as they have already served over the last two decades for the space programs of the world.

A vast amount of circuit technology for switching power supplies has been generated in the past decade, and reported in numerous technical journals, conference proceedings and trade magazines. Our understanding of this rapidly evolving technology can be greatly enhanced by the introduction of some meaningful classification technique which assists in recognizing and focusing on fundamental elements and characteristics. In this way, the most important but often subtle aspects of a particular subject are brought to the surface so as not

to become lost in the less important details. It has been found that such a classification scheme is indeed beneficial when working with the host of dcto-dc converters which have evolved over the past two decades.

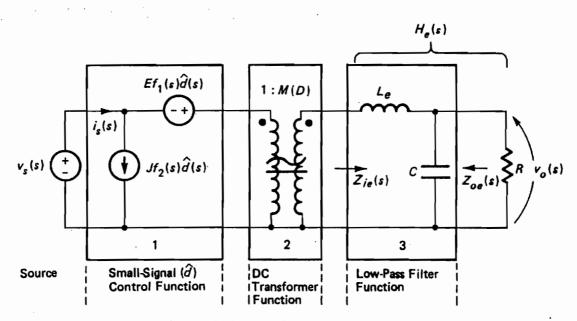

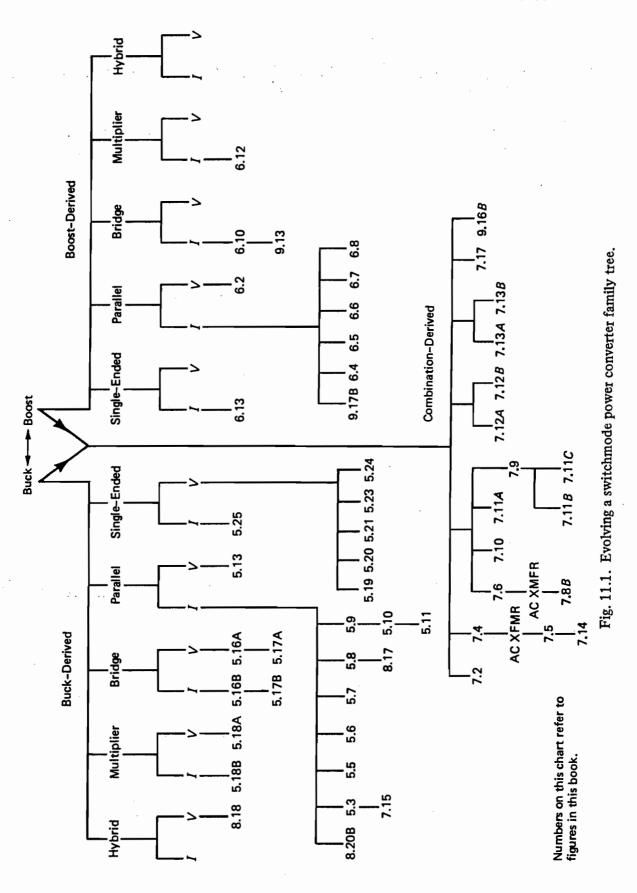

The authors have shown, for the first time, that a large class of the static dc-to-dc converters which are widely used in power processing applications fall within one of two families, namely, the buck-derived family and the boost-derived family. Each family is characterized by an equivalent averaged circuit model which exposes quite clearly the fundamental properties essential to the respective classes of converters. For example, the control-to-output transfer property of the boost-derived family of converter circuits exhibits non-minimum phase properties, i.e. a right-half S-plane zero, and two moving poles as the duty-cycle control signal is varied. The buck-derived converters, on the other hand, exhibit a zero and a double-pole which are both stationary. The differences in the fundamental properties that divide these two converter families are essential to the determination of a control strategy that assures loop stability and optimizes the dynamic responses.

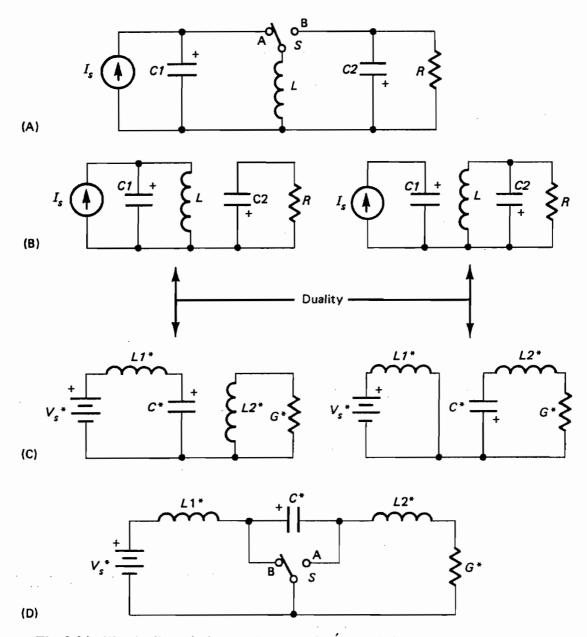

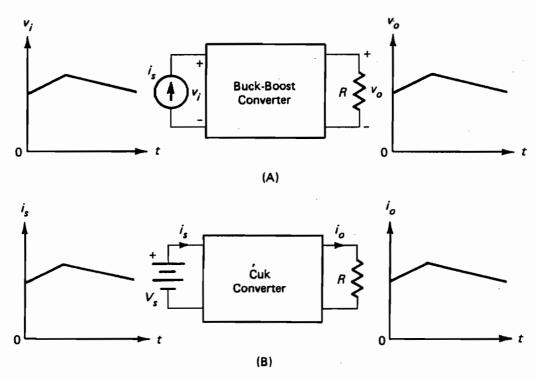

Based on this classification scheme, a third class of hybrid converters that share the properties of both buck and boost converters has become evident. The familiar buck/boost converter and Ćuk converter, for example, belong to the hybrid family. Through the introduction of the principle of duality relationship and bilateral inversion, a framework is established which makes evident natural relationships between converter families and enables a methodical transfer of knowledge gained about one family of converters to its dual counterpart. As a result of this classification structure and the duality relationships revealed through it, many new converter topologies are suggested.

Further, the authors present the idea of integrated magnetics and show that various magnetic components in a converter can be integrated in a simple magnetic core structure. It is demonstrated that the integrated magnetic concept can be applied in a generalized fashion to all converter circuits. The simplified magnetic circuits may have a profound impact in future converter design.

I am very pleased to see that the authors have successfully brought together a vast amount of circuit technology in a refreshing and well organized manner. This book, with its emphasis on switching mode power supply design and topology selection, will assist experienced design engineers and help to bring novices up to speed. Congratulations, Rudy and Ed, for a job well done.

FRED C. LEE

Professor

Department of Electrical Engineering

Virginia Polytechnic Institute

and State University

## **Preface**

From the everyday tools of science and business to the toys our children play with, no modern electronic product today goes untouched by the enormous strides made in microelectronic design technology over the past two and one-half decades. However, with each significant advance in micro-miniaturization of electronic systems has come a serious challenge to the designer of associated power processing networks to follow suit. These challenges are particularly difficult for those of us who must answer their call, for power processing techniques, as we know them today, are inherently discrete, by necessity physically larger than a user electronic system, and often wasteful in energy required to perform the processing or conditioning needed. This latter fact is especially true of those power processing schemes which utilize linear dissipative circuit approaches.

As the sizes of electronic systems began to shrink twenty years ago, it soon became very clear that bulky dissipative methods for power processing and conditioning would have to be replaced by more efficient and space-saving design techniques if overall product miniaturization was ever to be optimized. As a result, a new power electronics design specialty began to evolve, which has come to be known as the design of power conversion equipment using switch-mode power processing in conjunction with modern power semiconductors.

While the antecedents of this electronic design specialty clearly go back much earlier in time, it was the development of modern power semiconductors and the need for lightweight and efficient power processing equipment for space exploration programs that provided the initial impetus to explore and develop switch-mode conversion techniques. As is so often the case, it wasn't very long before military and, finally, commercial applications were being found for these switch-mode converter circuits (SPCs). In fact, today, in both dollar volume and unit numbers, the commercial use of SPCs has completely eclipsed their application in military and space electronic systems.

As a result of the widespread acceptance of SPCs, significant numbers of electronic engineers are now engaged in their design and application. It is not very surprising, given the ingenuity of the average electronic engineer, that literally

hundreds of SPC circuit variations exist, all of which can be used for electrical power processing. In addition, much has been learned about the fundamental behavior of these circuits. Most of their basic behavior can be presented rather simply, and in a manner which is of great practical interest to circuit designers.

A basic educational problem facing an electronics engineer new to this field has been the scattering of information concerned with the design of SPCs in hundreds of publications, patents, technical papers, correspondence internal to electronic firms, private memoranda, and other scientific reporting media. As a result, only a small portion of the practical information related to this specialty is common knowledge and in general use.

Because there is such a limited pool of public knowledge in this design art, 95% of SPC designs now in service use one of six topologies, or variations thereof, to perform the desired power processing. While these conventional circuit approaches have served well and are useful for many applications, they represent only a few out of literally hundreds of possibilities. Also, these few circuits are not necessarily the best choice for many of the applications in which they are being used.

Another effect of limited knowledge is the poor transient response of many converter systems to both input line and output load changes. This is frequently due to a less than complete understanding by designers of small-signal modeling and analysis methods for SPC circuits. This problem is so widespread that many SPC system designers and their users automatically assume that poor transient response is an inherent characteristic of these circuits when, in actuality, nothing could be further from the truth. Significant improvements in the methods of modeling and small signal characterization of SPC circuits have been made in the last ten years and highly accurate and easily applied representations are now possible. The combination of good dynamic system models, multi-loop control schemes, and high frequency switching can provide SPCs with transient response characteristics that rival conventional linear dissipative circuits.

The wide acceptance of SPC technology has led to an incredible variety of applications, many of which impose severe requirements. More often than not, today's SPC designer is faced with performance requirements that can only be fulfilled by circuit designs which fully exploit state-of-the-art technology. The old "business-as-usual" approach, employing one or two SPC circuit variations for all applications, is no longer viable. Increasing the output power level quickly brings the designer face-to-face with component stress limitations in conventional SPC topologies. The seemingly endless quest for physically smaller SPC systems often forces designers to use power switching rates in the hundreds of kilohertz to reduce size, a practice generally unheard of until the late 1970s. When properly and thoughtfully applied, the use of alternate circuit topologies can be a powerful tool for circumventing the problems presented by circuit component limitations as well as by operation at extraordinarily high frequencies.

New and more energy efficient power components continue to be developed and are finding widespread acceptance by SPC designers. The metal oxide semi-conductor field effect transistor (MOSFET) is a prime example of a new circuit element. While power MOSFETs can be successfully used in any conventional SPC circuit, alternative circuit topologies exist that take full advantage of the capabilities of these new semiconductors.

The motivation for this book is to gather as much of the current design knowledge concerning SPC circuits as possible in one place, and to present that knowledge in a direct and unified manner. Because the amount of available information is really quite voluminous, it is neither possible nor practical to restrict it to the contents of a single book. Therefore, in this text, we will restrict the discussion to the fundamental behavior and characteristics of SPCs and the many topological possibilities. The information presented herein is, in our opinion, that which is of the greatest utility to the designer of SPC circuits and systems. Therefore, we have deferred detailed discussion of component selection and the comprehensive design aspect of related system regulatory control to future texts in this power electronics series.

If we examine the present state of our understanding of SPC circuits, many gaps are readily discernible. In particular, a quantitative and accurate means for modeling and characterizing the large signal dynamic behavior of these circuits is still very much missing, although a concerted research and development effort is now in process to fill this void in our knowledge. It is very tempting to delay writing a book such as this one until all pieces of the SPC design puzzle have been found and put into place. No doubt, in a few years when the design art of SPCs has reached a level of considerable maturity, some excellent and highly definitive texts will be written on the subject. Unfortunately, many of us cannot afford to wait that long. So, despite its shortcomings, this text will still provide a broad introduction into the basic operation and characteristics of SPCs as well as into many of the more advanced aspects of SPC design.

This book is intended to be used both by electronics engineers just beginning to design SPC circuits and the old hands who have many years of experience in the field. Each will find much information which is useful for solving practical design problems. The text of the book is divided into two major sections. Section I (Chapters 1 through 11) presents the basic theory of SPC circuits as we understand them at this point in time. The presentation is straightforward with a minimum use of mathematics throughout, although some mathematical exercise is required in Chapters 2, 3, and 10 to support the ideas therein.

The discussions of Section I begin with the detailed exploration of two elementary SPC circuits to determine their large and small signal characteristics, and then builds progressively from these basic circuits to much more complex ones by using combinations of the basic circuits in conjunction with synthesis techniques.

The discussions of Section I assume the point of view that the desired power processing is voltage-related, that is, a voltage converter. This point of view could have just as well been current conversion-oriented and, in fact, we will see in Chapter 9 that these two points of view are duals electrically. The reason we have selected to pursue the voltage option is simply that this is by far the most common electrical conversion requirement encountered by SPC designers. The reader who has a need for a current converter should read Chapter 9 carefully, keeping in mind that the principles presented in that chapter can be applied to his requirement by the use of simple electrical duality relationships. Section I ends by discussing methods for comparing the relative merits of the multitude of SPC circuit topologies.

Section II (Chapter 12) is devoted to the examination of a variety of unique SPC circuits that fall into a special category of designs. This particular category encompasses converters whose primary inductive and transformer elements have been integrated (i.e., combined) into single physical assemblies. In many cases, the designs shown in Chapter 12, along with the methods behind the magnetic integration process, have never been shown or discussed before in any publication. Also contained in Chapter 12 is a brief review of magnetic fundamentals important to the understanding by the reader of the integration methods presented.

To further assist the reader, an extensive bibliography and lists of suggested reading materials has been included at the end of the book for reference and research purposes. We would like to acknowledge that only a portion of this book represents original contribution by the authors to the art of SPC design, with much of the information presented derived from the efforts of many others. The bibliography and reading list are attempts to acknowledge this fact. Of course, no practical reference list can ever be complete and, no doubt, many original contributions have been overlooked. To those individuals we have unintentionally omitted in this listing, we offer our sincere apologies for the oversight.

There are many individual researchers in the power electronics sciences who have distinguished themselves through their efforts to expand the design art of SPCs. In particular, we would like to acknowledge the work of Professor R. D. Middlebrook and his colleagues in the Power Electronics Group at the California Institute of Technology in Pasadena, California. Because of their dedicated research efforts, practical modeling and analysis of SPC systems is now feasible. Also, they have been instrumental in providing power electronics engineers with measurement tools and design techniques that have led to new SPC circuits and to a higher level of understanding of control techniques for SPCs than thought possible ten years ago.

A great deal of individual research into the science of power converter technology was required to write this text, including countless trips to the archives of many technical libraries and to facilities nationwide who maintain up-to-date records of SPC patents. Without the aid and assistance of Joy Bloom in the

preparation of this material, including over a year's effort of manuscript editing and processing, this book would not have been completed in a timely manner. We are certainly in debt to this very special lady.

Both of us are practicing electronic design engineers and the creation of this book has been an education and often a revelation on the overwhelming possibilities of SPC circuit variations. If reading this book opens up for you the new vistas and possibilities which we have discovered in writing it, then we will feel our efforts have been well spent.

G. E. Bloom R. P. Severns

# Contents

| FOREWORD by Fred C. Lee / vii<br>PREFACE / ix      |      |                                                            |  |  |

|----------------------------------------------------|------|------------------------------------------------------------|--|--|

| 1. INTRODUCTION TO SWITCHMODE POWER CONVERTERS / 1 |      |                                                            |  |  |

| 2. THE BUCK CONVERTER / 11                         |      |                                                            |  |  |

|                                                    | 2.1  | Buck Converter Operation / 12                              |  |  |

|                                                    | 2.2  | Steady-State Large-Signal Characterization / 18            |  |  |

|                                                    | 2.3  | Large-Signal Dynamic Characteristics / 29                  |  |  |

|                                                    | 2.4  | ,                                                          |  |  |

|                                                    | 2.5  | State-Space Averaged Model for the Discontinuous Mode / 43 |  |  |

| 3.                                                 | THE  | BOOST CONVERTER / 51                                       |  |  |

|                                                    | 3.1  | Boost Converter Operation / 51                             |  |  |

|                                                    | 3.2  | Large-Signal Steady-State Characterization / 55            |  |  |

|                                                    | 3.3  | Large-Signal Dynamic Characterization / 61                 |  |  |

|                                                    | 3.4  | State-Space Averaged Model for the Continuous Mode / 65    |  |  |

|                                                    | 3.5  | State-Space Averaged Model for the Discontinuous Mode / 73 |  |  |

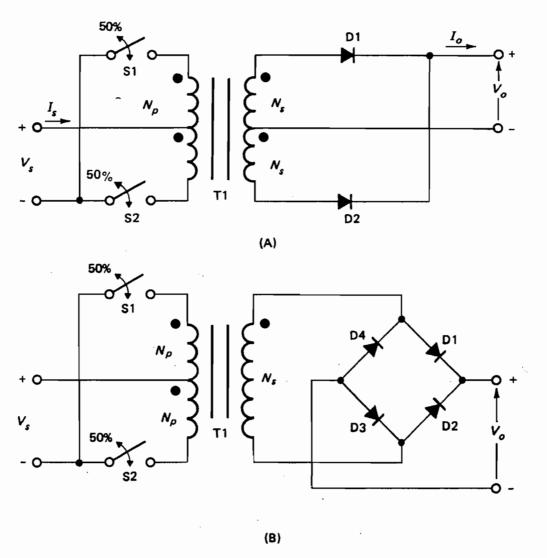

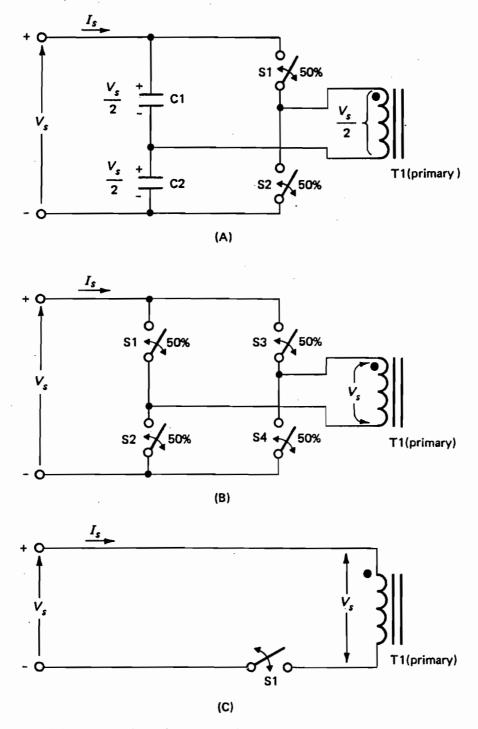

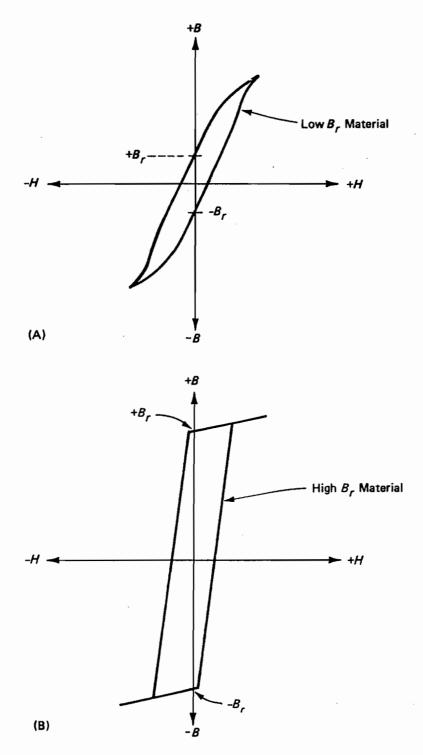

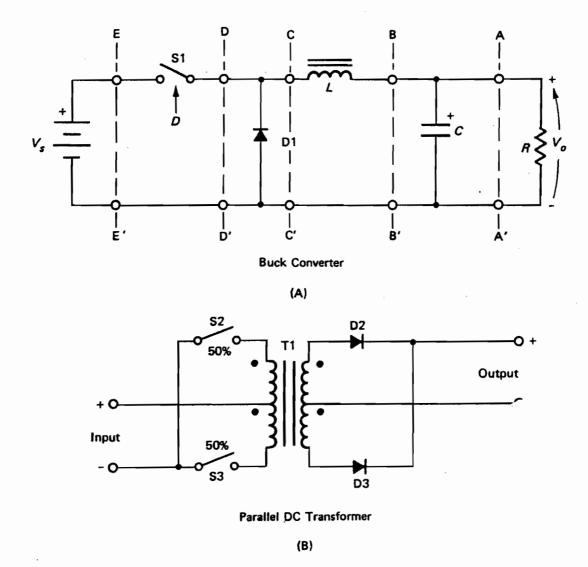

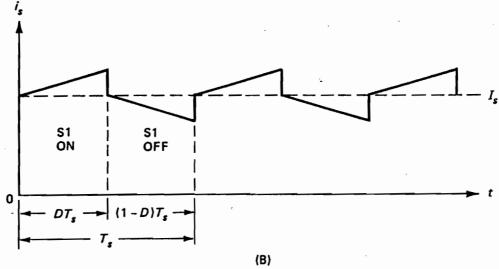

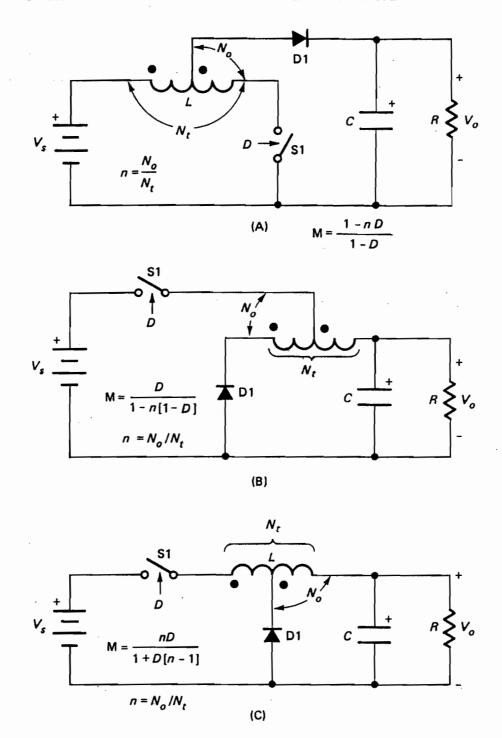

| 4. DC TRANSFORMERS / 78                            |      |                                                            |  |  |

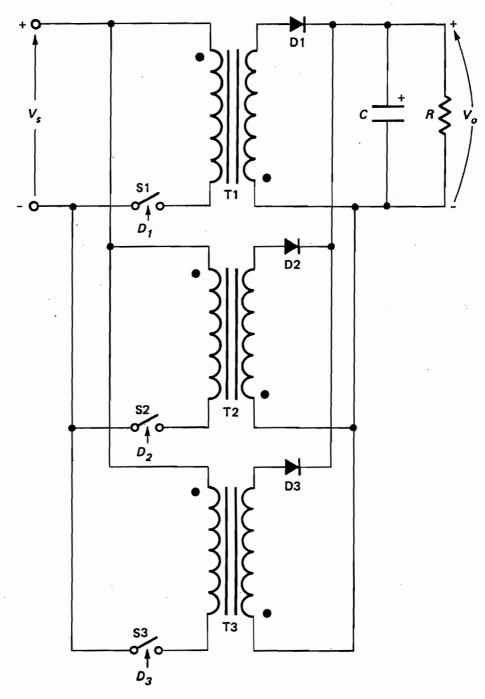

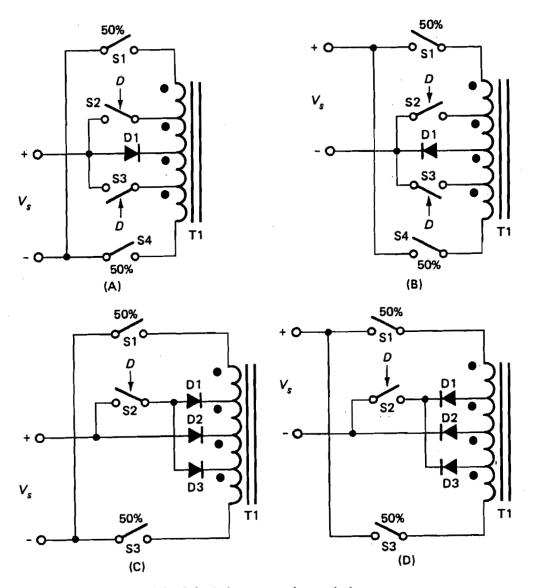

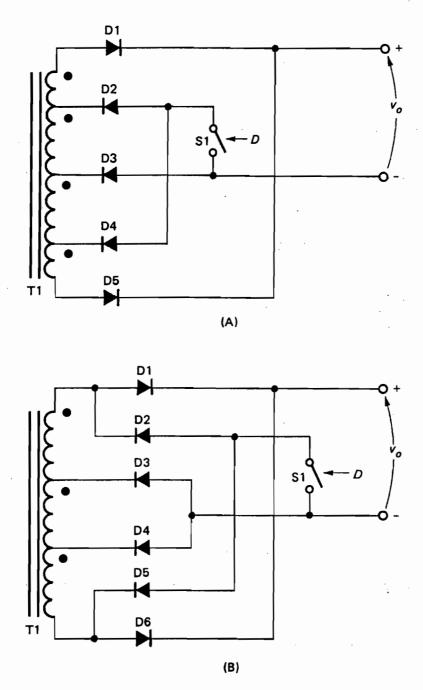

|                                                    | 4.1  | Typical Configurations / 78                                |  |  |

|                                                    | 4.2  |                                                            |  |  |

|                                                    | 4.3  | Bidirectional Power Flow / 94                              |  |  |

|                                                    | 4.4  | ,                                                          |  |  |

|                                                    | 4.5  | Source Impedance Effects / 108                             |  |  |

|                                                    | . ,0 | 7 200                                                      |  |  |

| xvi | CON  | TENTS                                                                                                                                                                  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

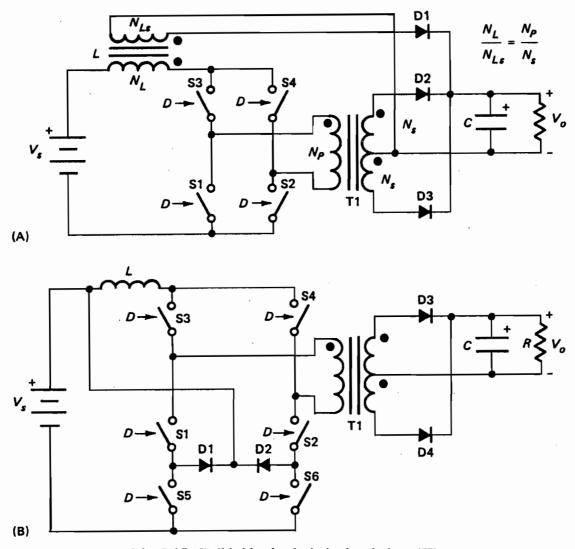

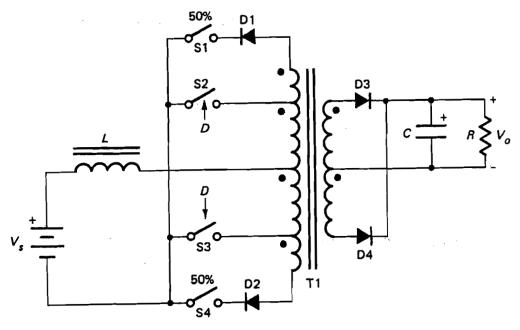

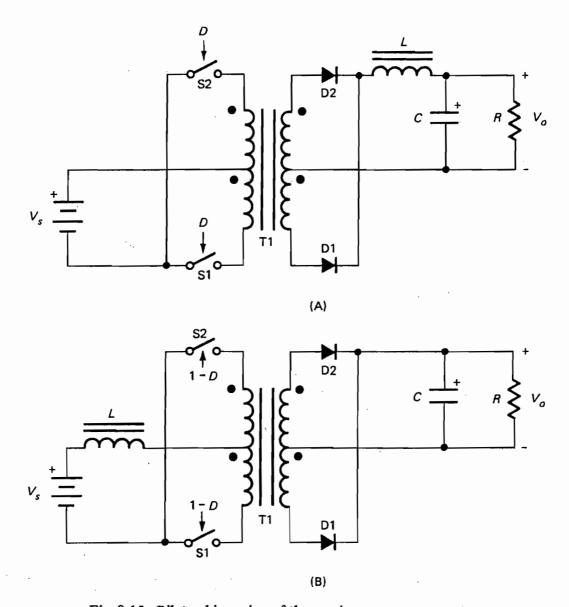

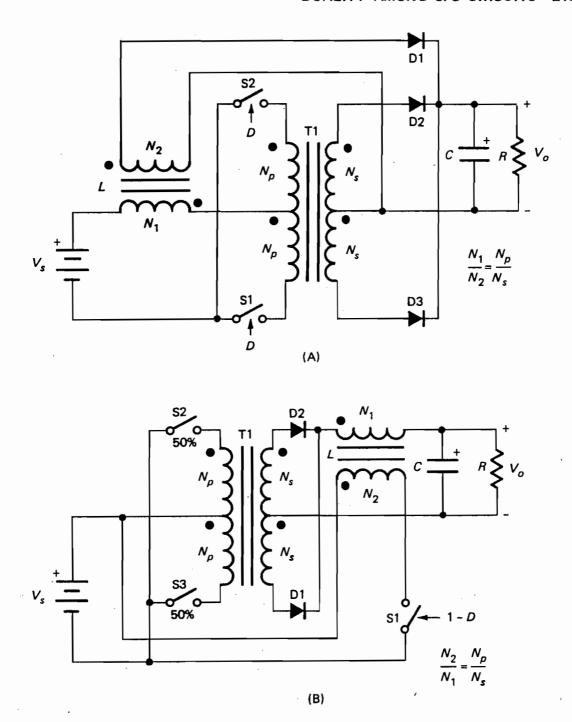

| 5.  | BUCK | C-DERIVED CIRCUITS / 112                                                                                                                                               |

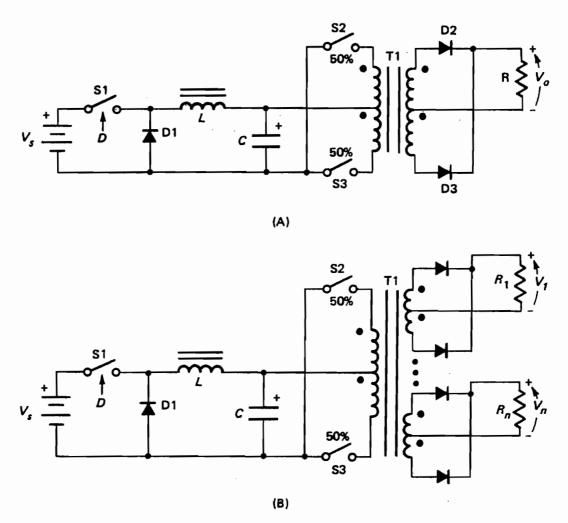

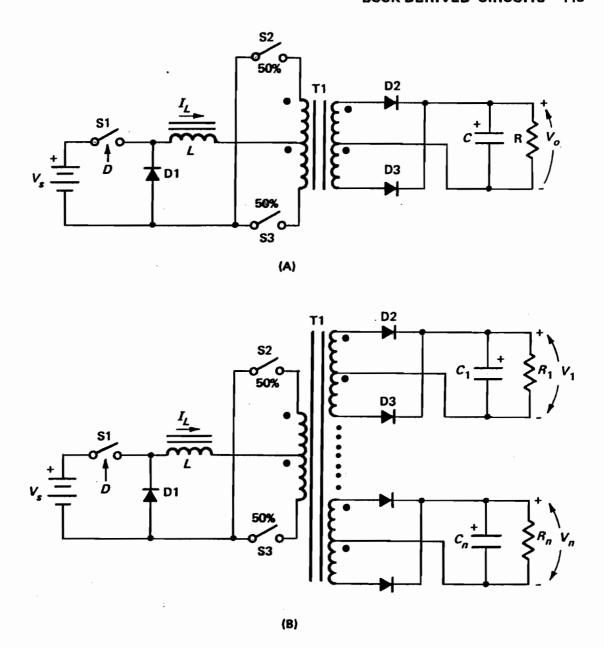

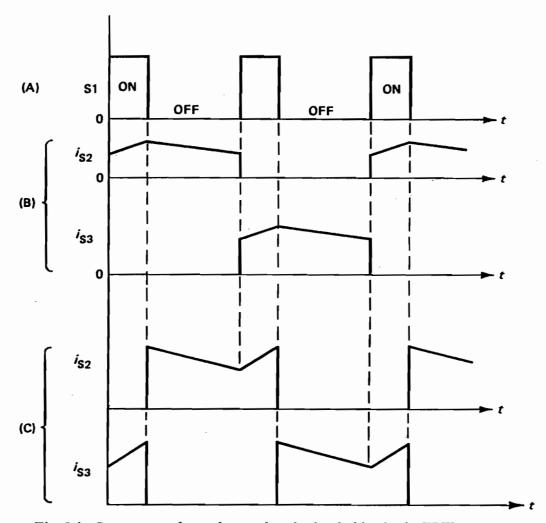

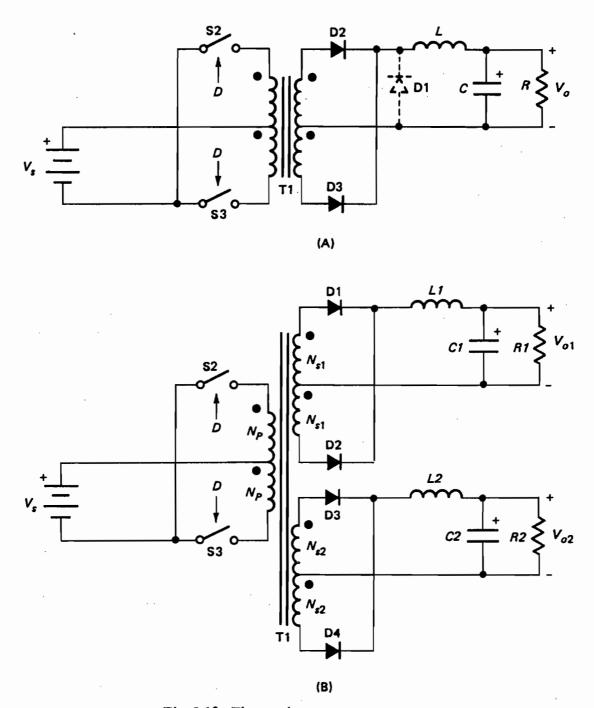

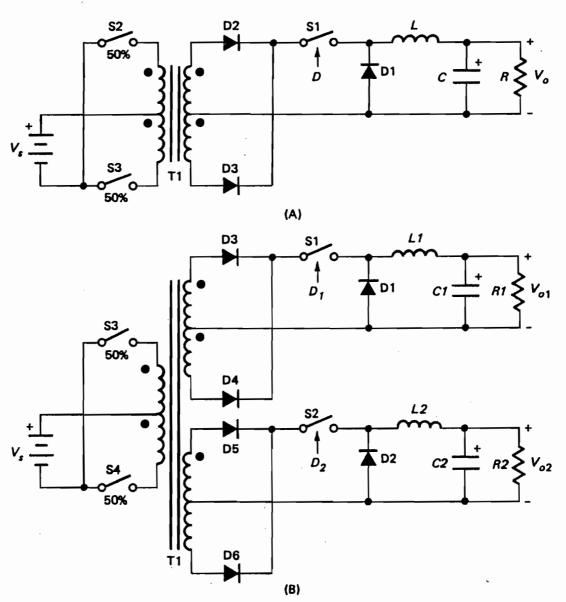

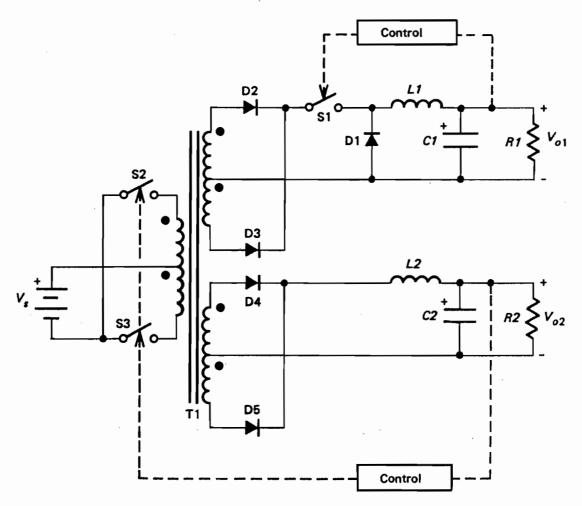

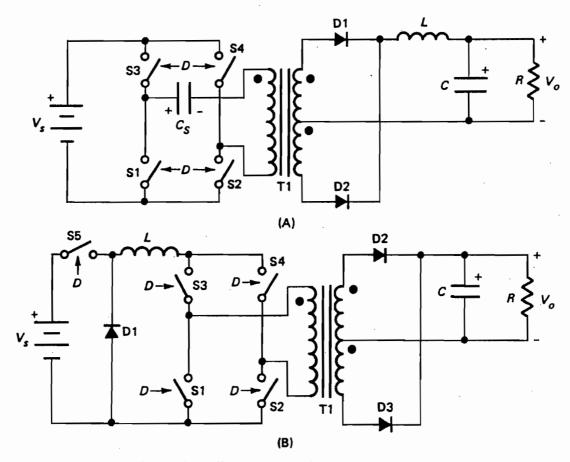

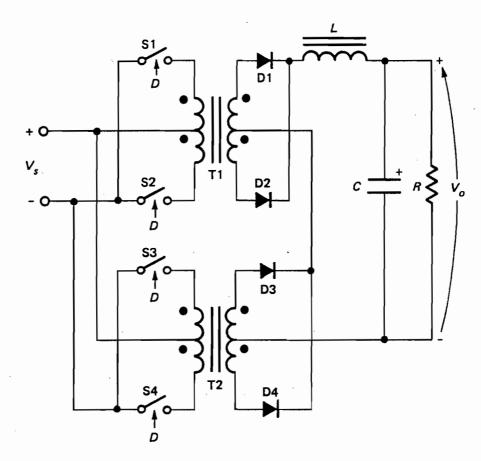

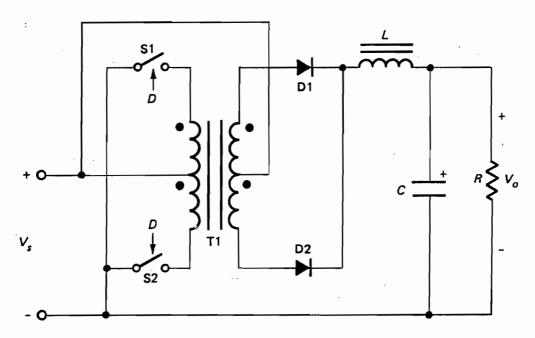

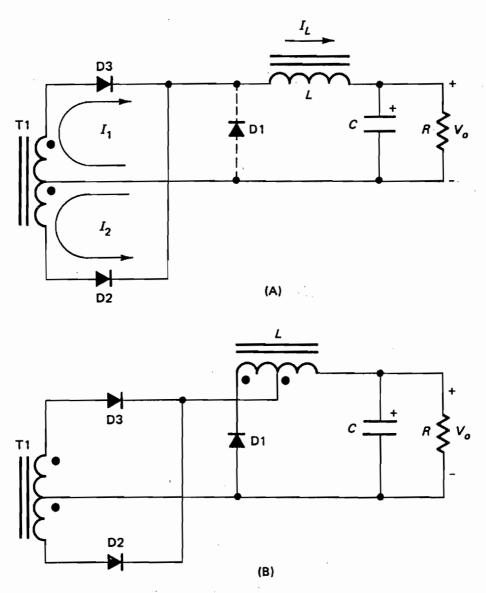

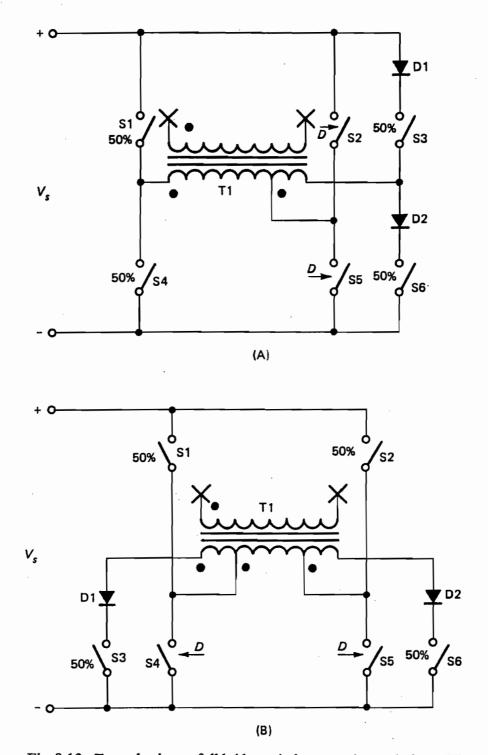

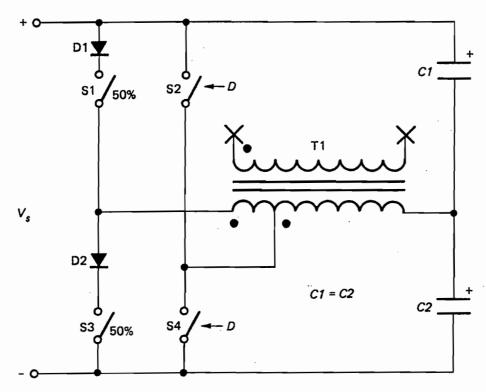

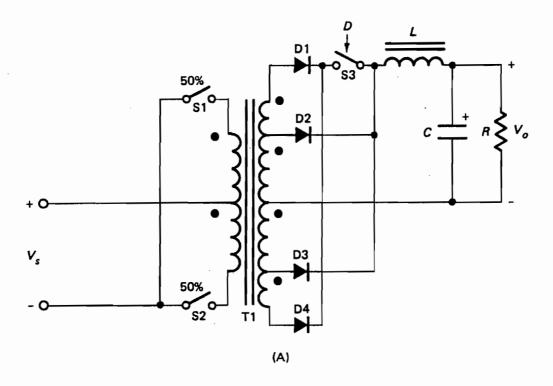

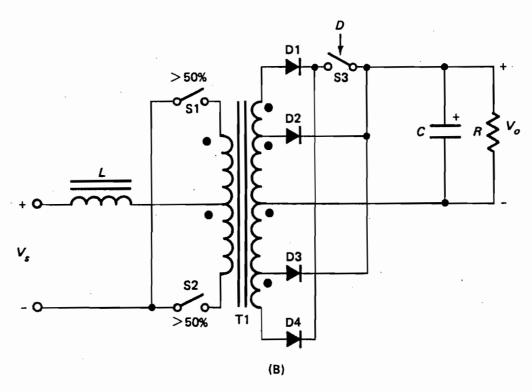

|     | 5.2  | Buck SPC and Parallel Transformer Combinations / 112 Full- and Half-Bridge DC Transformers in the Buck SPC / 128 The Single-Ended DC Transformer in the Buck SPC / 130 |

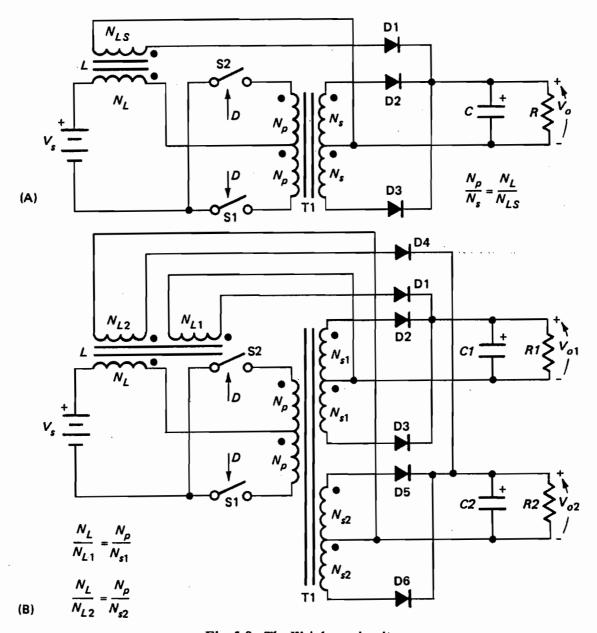

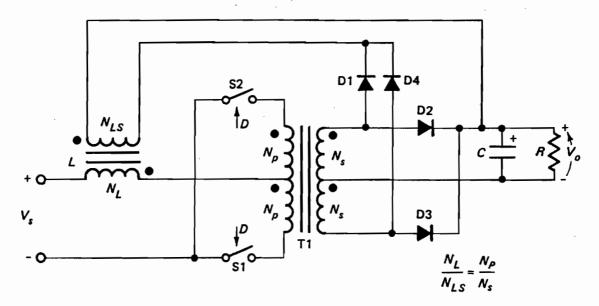

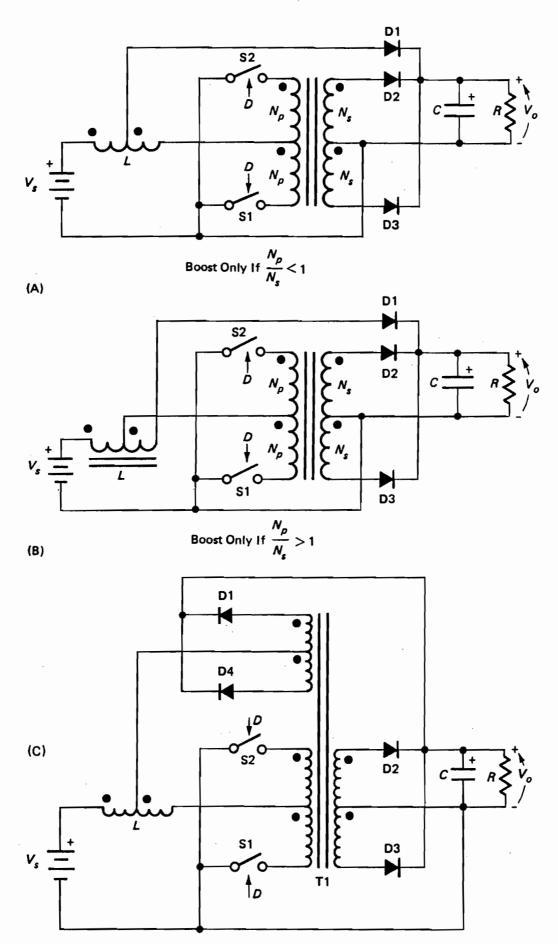

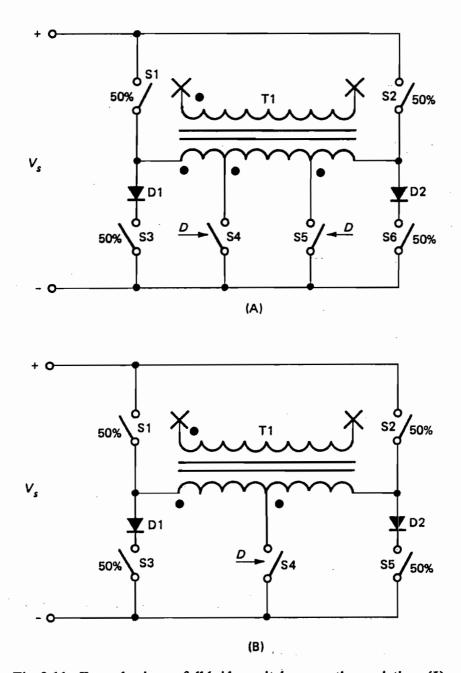

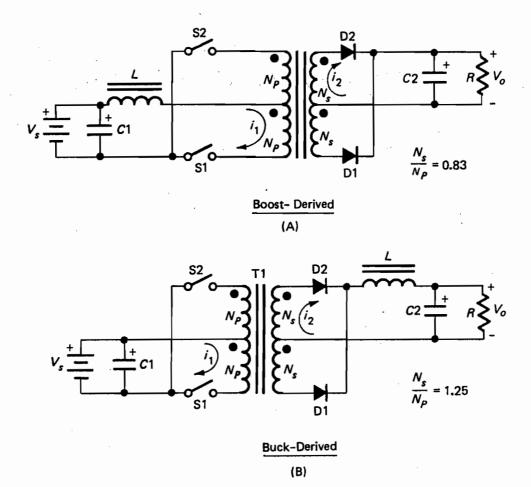

| 6.  | BOOS | T-DERIVED CIRCUITS / 136                                                                                                                                               |

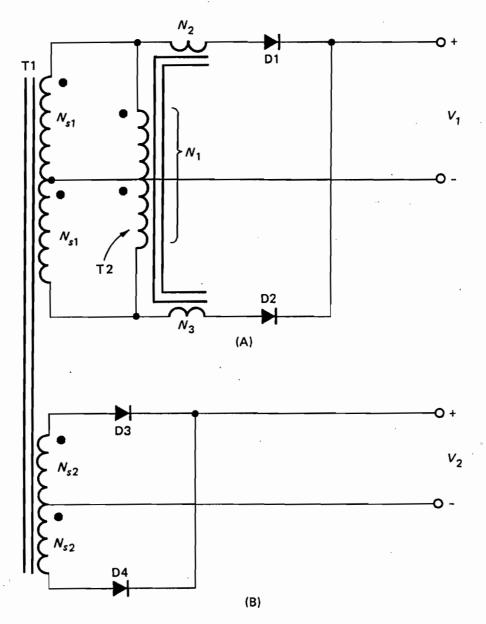

|     |      | Parallel DC Transformers Within Boost Converters / 136<br>Bridge and Half-Bridge DC Transformers Within Boost<br>Converters / 146                                      |

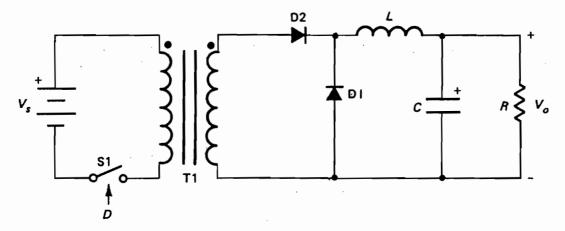

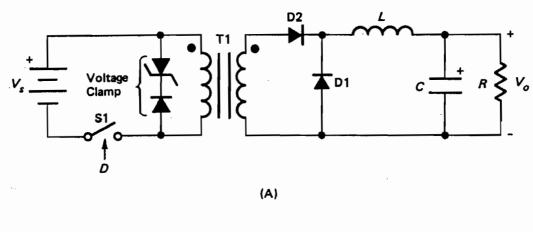

|     | 6.3  | Single-Ended DC Transformers Within Boost Converters / 150                                                                                                             |

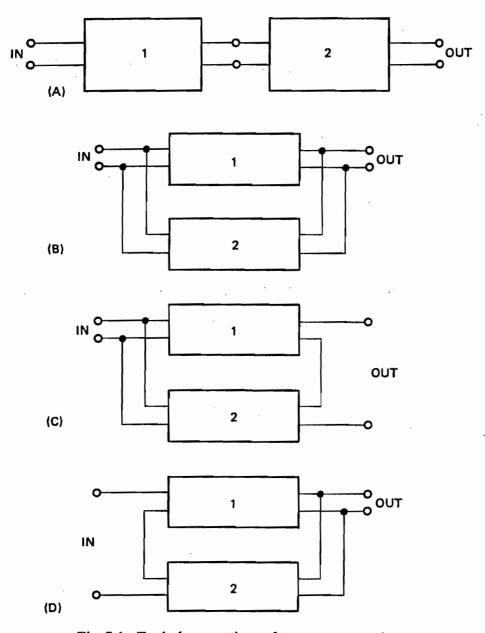

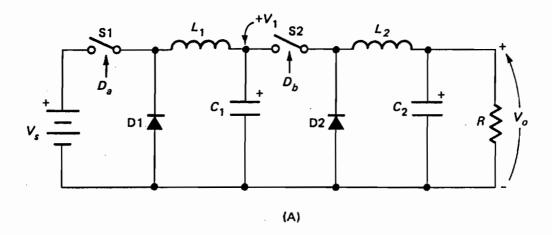

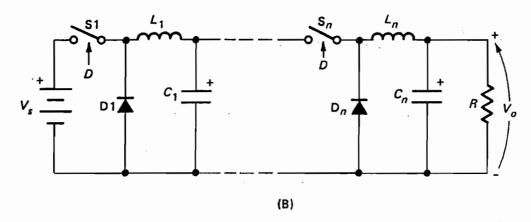

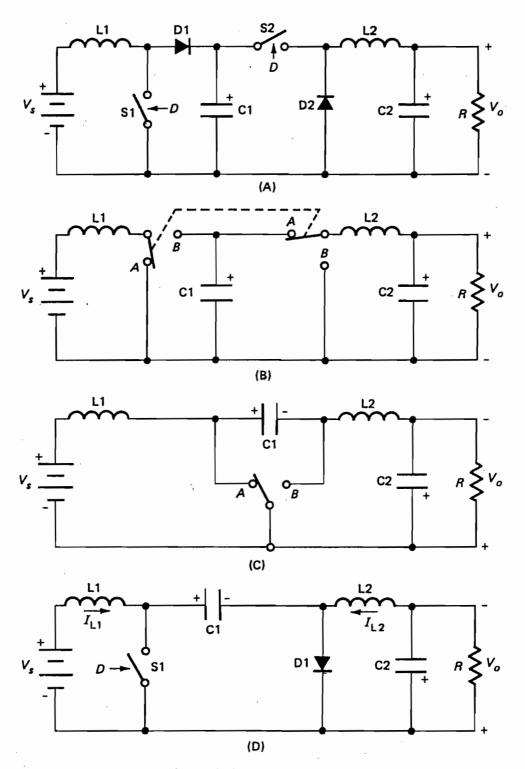

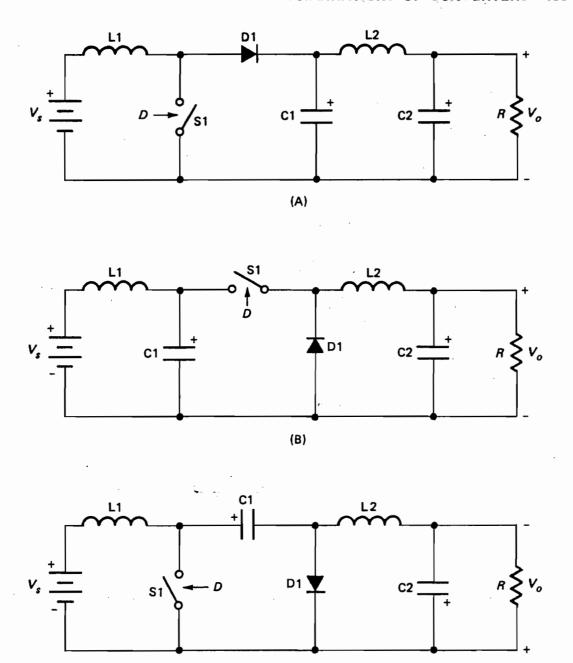

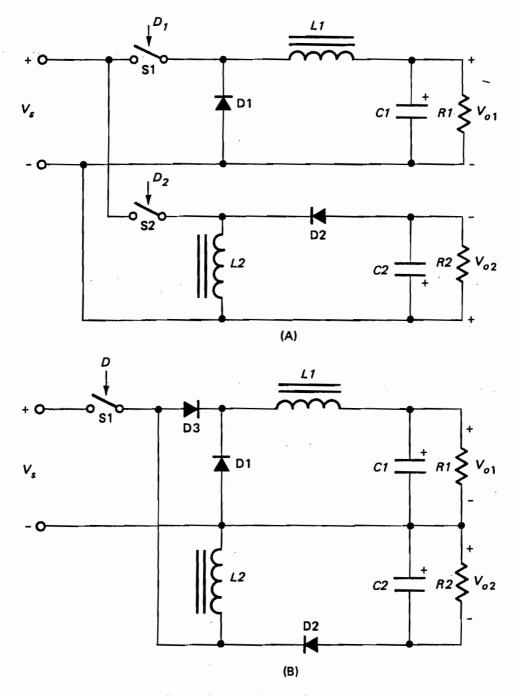

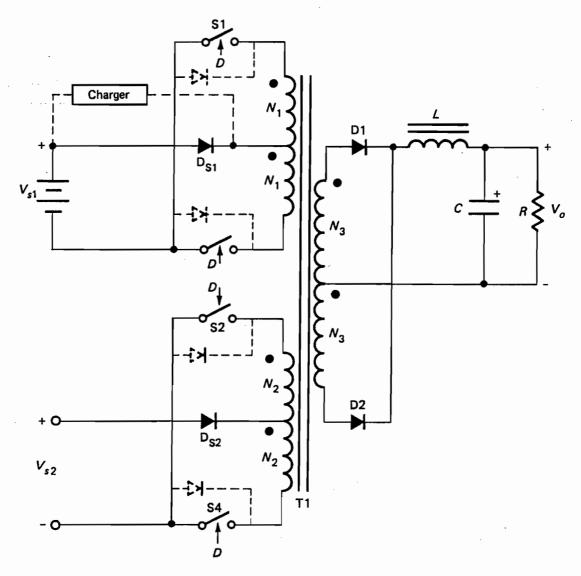

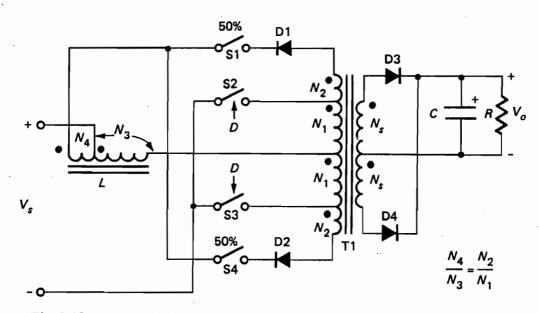

| 7.  | COMI | BINATIONS OF CONVERTERS / 153                                                                                                                                          |

|     | 7.1  | Cascading Identical Converters / 153                                                                                                                                   |

|     | 7.2  | Cascading Dissimilar Converters / 156                                                                                                                                  |

|     | 7.3  | Paralleling Converters / 169                                                                                                                                           |

|     | 7.4  | Other SPC Combinations / 171                                                                                                                                           |

| 8.  | MAGI | NETIC COMPONENT TAPPING / 173                                                                                                                                          |

|     | 8.1  | Inductor Tapping / 175                                                                                                                                                 |

|     |      | Transformer Winding Taps / 183                                                                                                                                         |

|     |      | Combining Transformer and Inductor Tapping Methods / 193                                                                                                               |

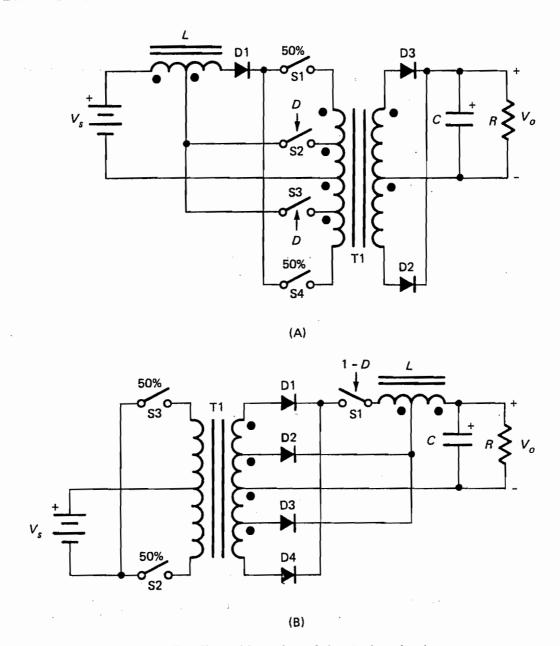

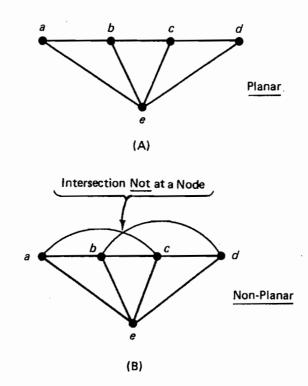

| 9.  | DUA  | LITY AMONG SPC CIRCUITS / 199                                                                                                                                          |

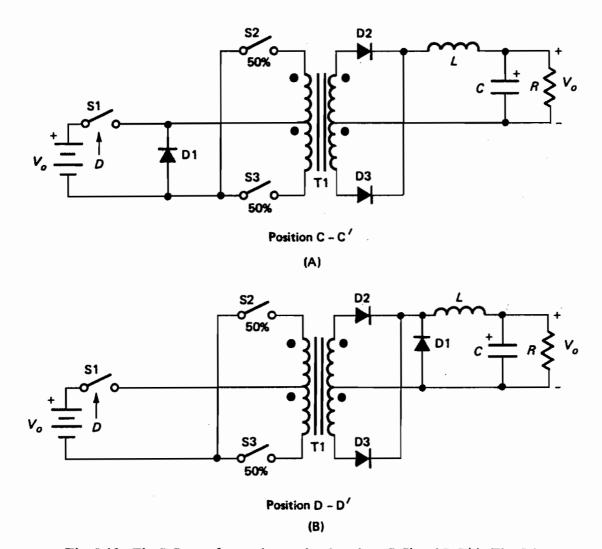

|     | 9.1  | Bilateral Inversion / 199                                                                                                                                              |

|     | 9.2  | Inversion of Rectifier Networks / 202                                                                                                                                  |

|     | 9.3  | Topology Modification by Switching Sequence Variations / 211                                                                                                           |

|     | 9.4  | Applying Bilateral Inversion to Complex Converters / 215                                                                                                               |

|     | 9.5  | Applying the General Duality Principle to SPC Circuits / 218                                                                                                           |

| ٠   | 9.6  | Applying Duality to SPC Circuits / 226                                                                                                                                 |

|     | 9.7  | Duality in Inductive and Capacitive Energy Transfer / 229                                                                                                              |

| 10. |      | LL-SIGNAL MODELS OF COMPLEX CONVERTERS AND ULATORS / 231                                                                                                               |

| -   | 10.1 | The Canonical Model / 231                                                                                                                                              |

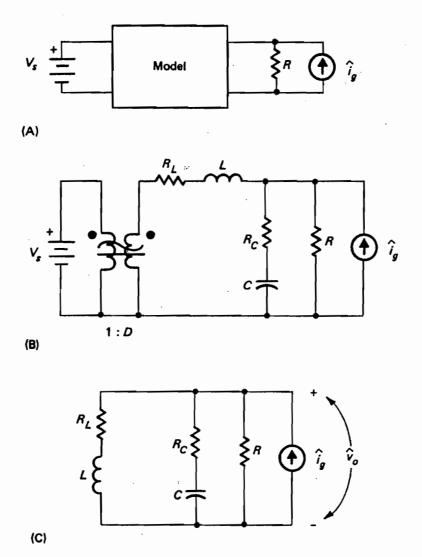

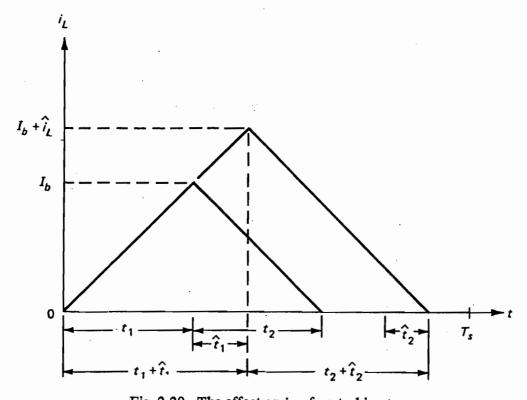

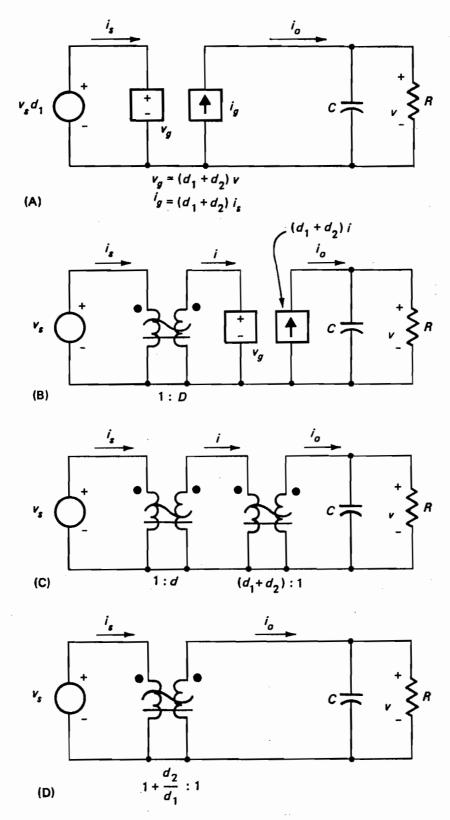

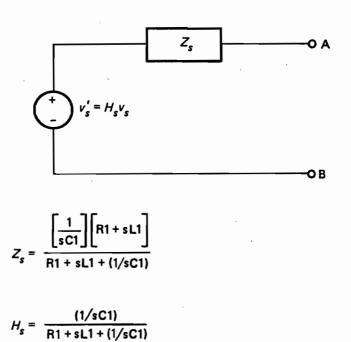

Models for Complex Converters / 239

Closing the Loop / 248

10.2

10.3

| 11. | COMPARATIVE TECHNIQUES FOR SPC SELECTION / 254 |                                                           |

|-----|------------------------------------------------|-----------------------------------------------------------|

|     | 11.1<br>11.2<br>11.3                           |                                                           |

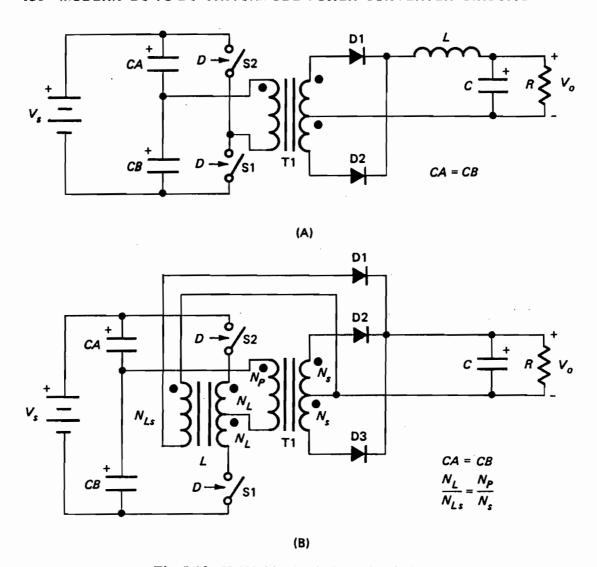

| 12. | CONV                                           | VERTERS WITH INTEGRATED MAGNETICS / 262                   |

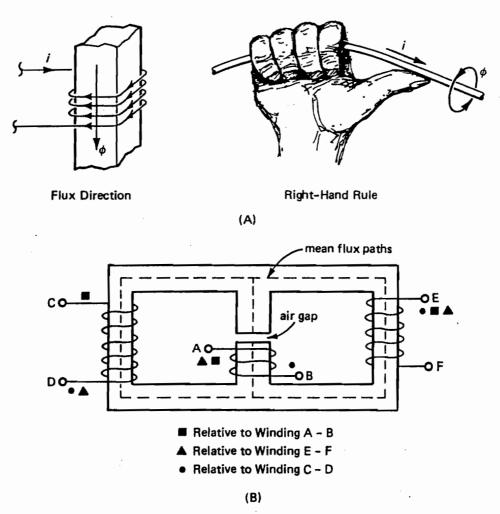

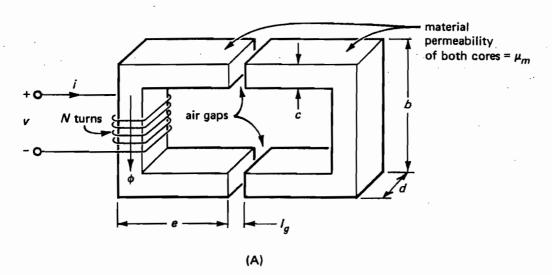

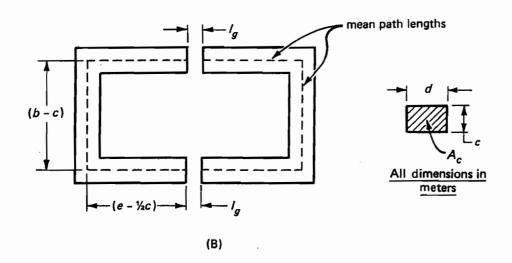

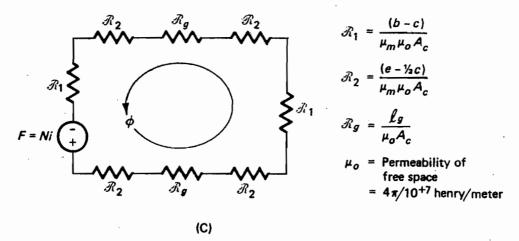

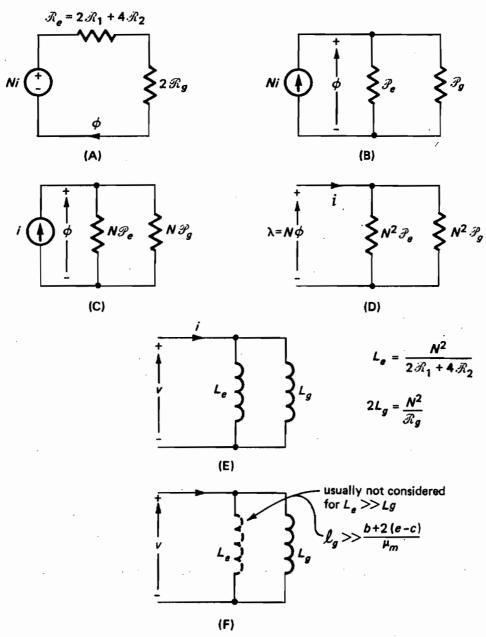

|     | 12.1                                           | Magnetic Circuit Analysis—A Review of Concepts / 263      |

|     | 12.2                                           | Examples of Magnetic Circuit Models / 266                 |

|     | 12.3                                           | Two-Winding Inductors and the Zero-Ripple Current         |

|     |                                                | Phenomenon / 273                                          |

|     | 12.4                                           | Application in Basic Converters / 280                     |

|     | 12.5                                           | Three-Winding Inductors and the Zero-Ripple Current       |

|     |                                                | Phenomenon / 282                                          |

|     | 12.6                                           | More Zero-Ripple Converter Applications / 291             |

|     | 12.7                                           | A Forward Converter with Integrated Magnetics / 294       |

|     | 12.8                                           | An Isolated Boost SPC with Integrated Magnetics / 303     |

|     | 12.9                                           | Rudimentary Synthesis Methods / 304                       |

|     | 12.10                                          | More Complex Converters with Integrated Magnetics / 309   |

|     | 12.11                                          | Small-Signal Modeling Considerations / 317                |

|     | 12.12                                          | Ripple Current Control for Buck and Boost Converters with |

|     |                                                | Integrated Magnetics / 318                                |

#### BIBLIOGRAPHY / 325

#### SUGGESTED READING AND OTHER INFORMATION SOURCES / 330

12.13 Cautions in Designing Integrated Magnetic Converters / 321

- 1. Conference Records / 330

- 2. Technical Books / 331

- 3. Magazines, Journals and Periodicals / 332

- 4. Patent Files / 333

#### INDEX / 335

MODERN

DC-TO-DC

SWITCHMODE

POWER

CONVERTER

CIRCUITS

# 1. Introduction to Switchmode Power Converters

In a general sense, a power converter can be defined as a device which converts one form of energy into another on a continuous basis. Any storage or loss of energy within such a system while it is performing its conversion function is usually incidental to the process of energy translation. There are many types of devices which can provide such a function with varying degrees of cost, reliability, complexity and efficiency.

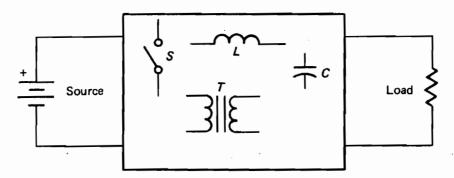

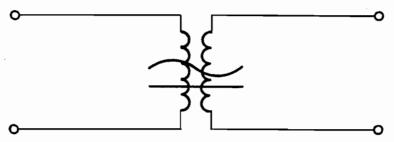

The mechanisms for power conversion can take many basic forms, such as those which are mechanical, electrical, or chemical in processing nature. We will be concerned here only with power converters which perform energy translation electrically and in a dynamic fashion, using the limited variety of components collectively illustrated in Fig. 1.1. How these circuit components are interconnected will be determined by the power translation desired. We restrict our choice of electrical components to include only inductors, capacitors, transformers, and switches, intentionally omitting resistors because they introduce undesirable power losses. High efficiency is usually an overriding requirement in most applications for electronic switchmode power converter (SPC) circuits, so resistive circuit elements must be avoided. This is not to say that resistances do not exist in SPCs. In their physically realizable forms, none of our chosen circuit components are ideal and all will introduce some resistive loss in the conversion process. However, every effort is made by SPC designers to minimize these parasitic resistances so that their presence and influence on SPC efficiency and conversion performance will not be significant. Only on rare occasions and for very special reasons are power consuming resistances introduced into the main power control paths of an SPC circuit. In auxiliary circuits, such as sequence, monitor, and control electronics of a total SPC system, high value resistors are commonplace, since their loss contributions are usually insignificant.

In SPC circuits, the semiconductor switches controlling the dynamic transfer of power from input to output are either fully ON or fully OFF, with very short transition times from one of these states to the other. Component voltage wave-

#### 2 MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

Fig. 1.1. Switchmode power converter components.

form shapes take the forms of either periodic pulse-width-modulated (PWM) rectangles, square waves, or combinations thereof. The associated current waveform shapes are usually triangular to trapezoidal. Semiconductor parts normally employed as switching elements in SPCs are fast recovery diodes, bipolar junction transistors (BJT), metal oxide semiconductor field effect transistors (MOSFET) and gate turn-off thyristors (GTO).

The most general form of the conversion function would be the transformation of a source of polyphase AC potential of one magnitude, phase, and frequency to another magnitude, phase, or frequency. With this concept, a DC input or output of an electrical power converter system can be viewed as AC with zero frequency and phase.

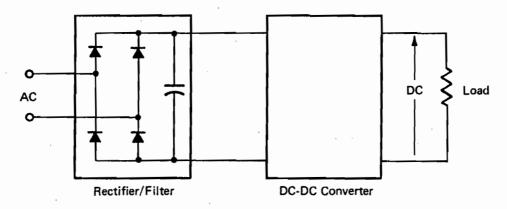

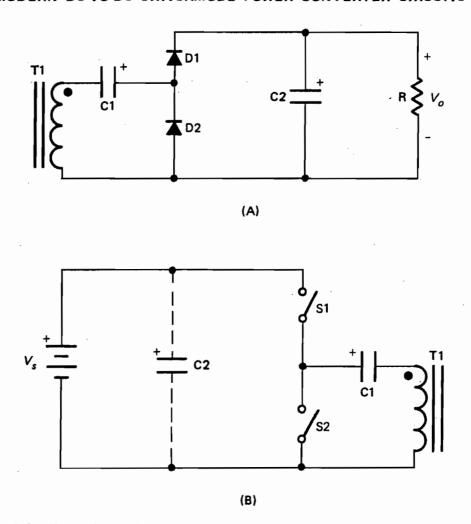

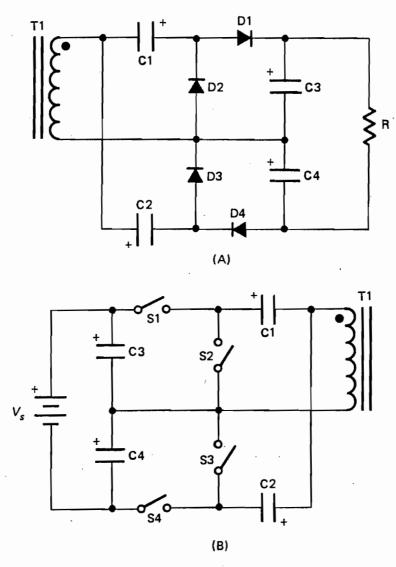

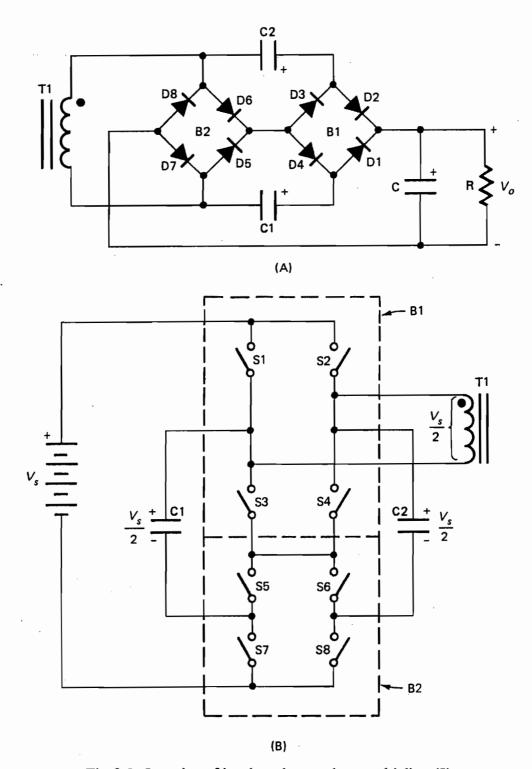

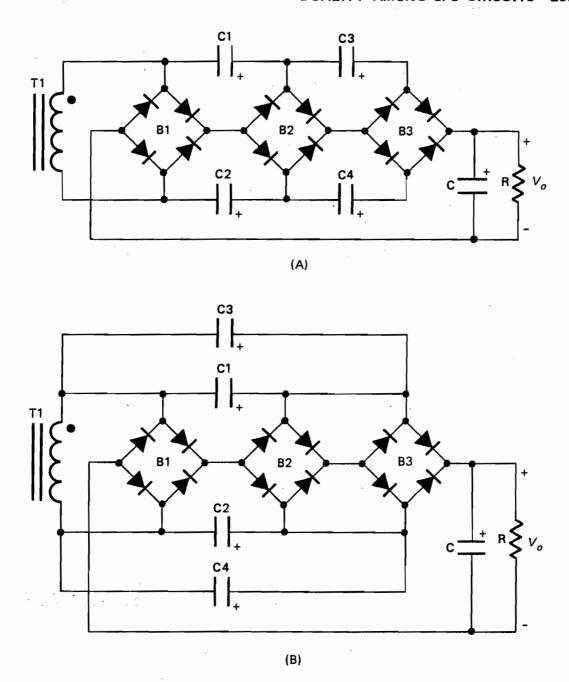

The discussions in this book will be limited to those circuits which perform a dynamic DC to DC (DC-DC) power conversion function. This is not nearly as restrictive a view as it might first appear, since there are a great many applications for a DC-DC SPC. There are also a large number of applications for AC to DC (AC-DC) conversion. This latter function is usually implemented by preceding a DC-DC converter circuit with a simple rectifier-filter network, a typical example of which is shown in Fig. 1.2. DC to AC and AC to AC power converter systems frequently use AC-DC and DC-DC networks as subsystem elements working together to obtain the desired output characteristics.

Fig. 1.2. Typical implementation of AC-to-DC conversion.

It is also interesting to note that many motor control systems use circuit components and topologies that closely resemble DC-DC converters. If we consider the uniform rotary and, in some cases, linear output from a motor to be equivalent to a DC output, then the motor and its controller network can be viewed as a DC-DC or AC-DC converter. It follows then that a great deal of the design technology related to DC-DC converters is directly applicable to motor control electronics. For reasons such as this, a study of DC-DC converters using SPC techniques is very worthwhile and has wide applicability to other related power control disciplines.

Many virtues are expected of-electrical power converters. They must be highly efficient, occupy little volume, be low in cost and weight, and have a long service life with no failures. Often their outputs must be regulated to close tolerances, even though their inputs may vary over a very wide range of values. The family of SPC circuits, which we will explore in this text, are able to fulfill these requirements remarkably well, provided their designs are well executed.

Depending on application needs, a DC-DC SPC circuit could be very simple in form, using only one SPDT switch, one inductor, and one capacitor. On the other hand, it may be very complex, utilizing many components to accomplish the required DC conversion function. Regardless of the complexity of a particular SPC circuit, the following key idea always applies:

#### Key Idea #1

THE INDUCTORS AND CAPACITORS OF A DC-DC SPC MUST, IN SOME MANNER, FORM A LOW-PASS FILTER NETWORK.

The justification for this idea is the need for a DC output voltage with a minimum of superimposed AC ripple from the switching action of an SPC. Since the internal nodal or branch waveforms of an SPC are at some point pulsating with both AC and DC components, a low-pass filter is required to prevent the undesirable AC components produced by SPC switching action from appearing at the output terminals of the converter.

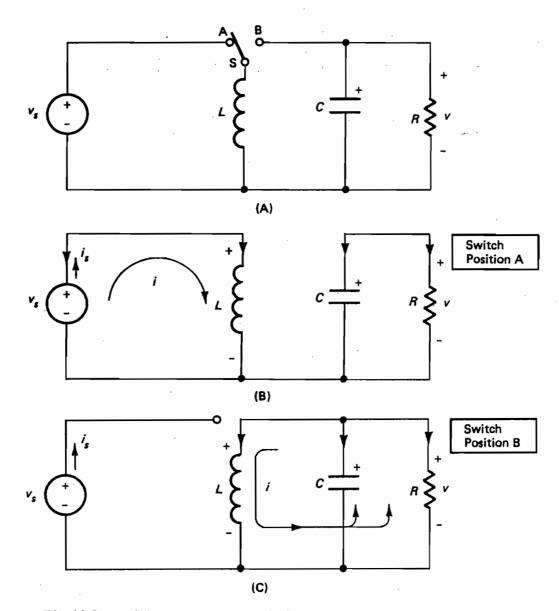

It is not always easy to isolate the low-pass inductive and capacitive filter elements of an SPC from a casual inspection of its circuit diagram, since the effective filter inductor element (or elements) is often separated from the filter capacitor element (or elements) by switches and/or transformers. In the modeling processes to be discussed in Chapters 2, 3, and 10, we will invariably derive an equivalent low-pass filter network for each converter type. The most common circuits have a single-section low-pass filter. However, there are some special SPC circuits (such as the Cuk SPC) which contain multiple-section equivalent filter networks.

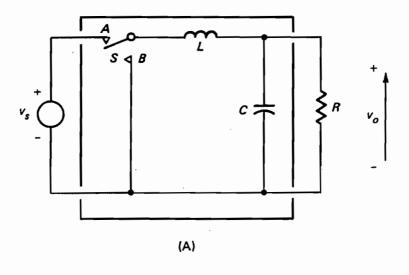

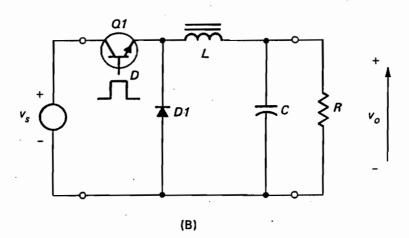

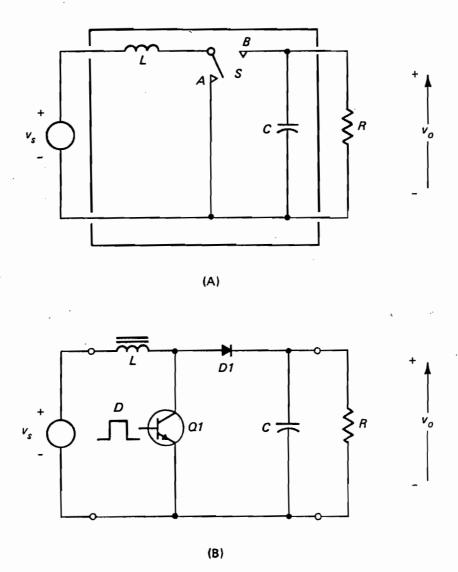

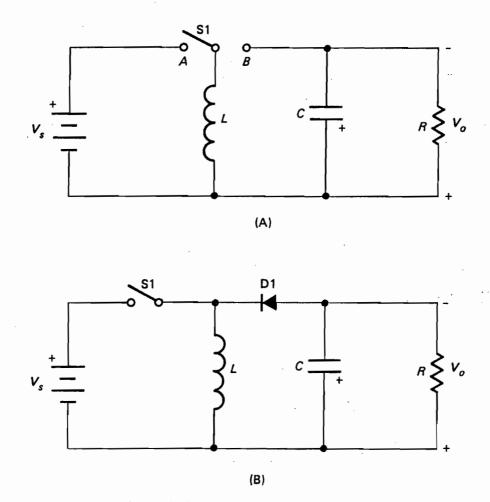

Two of the simplest SPCs are shown in Figs. 1.3 and 1.4, along with physical realizations for their SPDT switch functions (Figs. 1.3B and 1.4B). The circuit

#### 4 MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

Fig. 1.3. The buck converter.

in Fig. 1.3 is called a buck (step-down) converter because the output voltage is always less than the input voltage. The circuit of Fig. 1.4 is referred to as a boost (step-up) converter because its output voltage is always greater than the input voltage.

One point should be made here. The output capacitor (C) in the buck converter is not absolutely essential for the circuit to function properly, since its inductor (L) and load resistor (R) form a low-pass filter by themselves and, in theory at least, L can be made arbitrarily large in value to produce a small ripple current in R. However, even the presence of a small amount of output capacitance will greatly reduce the size of L required to obtain a DC output voltage across R with a minimal AC ripple. In actual practice, C is rarely omitted. For this reason, we will assume that the basic buck converter will usually possess an output filter capacitor. On the other hand, the output capacitor of the boost converter cannot be omitted, since the output current will always be pulsating even if the inductor is infinitely large. Thus, to obtain a low-ripple output voltage,

Fig. 1.4. The boost converter.

a filter capacitor is always necessary across the output terminals of a boost converter.

We will now put forward a number of additional key ideas regarding SPCs in general.

#### Key Idea #2

ALL KNOWN DC-DC SPC CIRCUITS CAN BE DERIVED FROM COMBINATIONS OF BUCK AND/OR BOOST CONVERTERS ALONG WITH SOME FORM OF TRANSFORMATION FUNCTION.

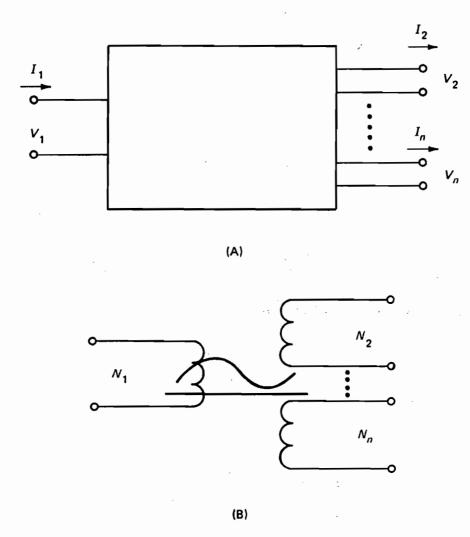

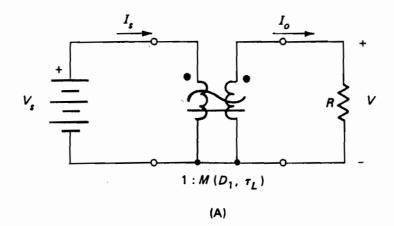

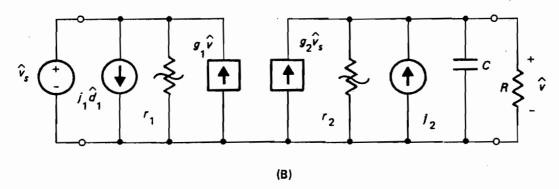

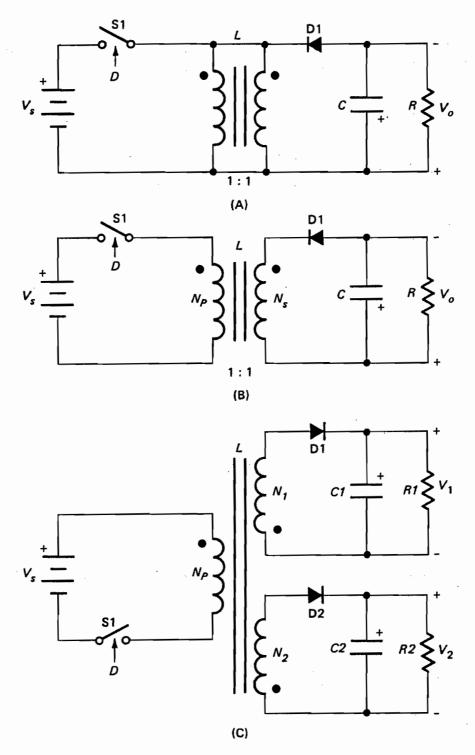

The transformation function is shown in a general fashion in Fig. 1.5A, and can be characterized as an ideal transformer element, as illustrated in Fig. 1.5B. Because of its ideal properties, such an element can transform DC as well as AC.

#### 6 MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

Fig. 1.5. The ideal transformation function.

Obviously, an ideal transformer element would be very difficult to realize in actual practice. Fortunately, perfection is not usually required in transforming voltages and currents within SPCs, and there are many practical design approximations which serve quite well. This subject of both DC and AC transformation will be treated in more detail in Chapter 4.

The justification for the assertion in Key Idea #2 is strictly empirical, i.e., no SPC circuit known at this point in time is so complex that it cannot be reduced to a combination of these elementary circuits. In the discussion that follows, the truth of this key idea is assumed and the structure of this book is organized in accordance with this premise. Chapters 2 through 4 will examine the two basic SPC converter circuits and transformation elements in great detail. That material will then be used in later chapters to examine more complex converter structures.

A third key idea is directly related to the second one:

#### Key Idea #3

THE PROPERTIES OF BASIC CONSTITUENT CONVERTERS (i.e., buck and/or boost) ARE RETAINED IN ANY COMPLEX DERIVA-TIVE CONVERTER SYSTEM.

This key idea holds for the majority of complex SPCs, with the exception of a few converter circuits which use tapped inductors and transformers with equal turns ratios between windings. In some of these special converters, basic behavior patterns are modified to some extent. This subject is discussed in Chapter 10. Except for these special exceptions, the above idea is sound and the general properties of a complex SPC can be readily predicted from a knowledge of its basic constituents. This ability to directly relate circuit properties of many SPCs is a valuable tool in comparing the merits of more complex circuits.

For example, if one needs an SPC with inrush and short-circuit current control capabilities like those exhibited by a buck SPC, he must use an SPC topology that is buck-derived. By its very nature, an unmodified boost-derived converter cannot provide such current-control features. When one attempts to modify a boost-derived converter to include these features, one of two things will happen. The modified circuit will either become a buck-derived SPC or it will exhibit either buck-derived or boost-derived characteristics, depending on input voltage and output current magnitudes. Examples of SPCs which can have this type of dual personality are discussed in more detail in Chapter 9.

A fourth key idea which is of practical importance to an SPC designer is:

#### Key Idea #4

NO SINGLE SPC CIRCUIT TOPOLOGY IS ELECTRICALLY IDEAL FOR ALL APPLICATIONS. IT IS THE PARTICULAR APPLICATION WITH ITS INDIVIDUAL REQUIREMENTS THAT DETERMINES WHICH CIRCUIT WILL BE THE BEST TO USE.

This may seem to be a very obvious, almost trivial statement. However, even a brief look at the claims (and often the practice) within the power electronics industry will reveal that this simple truth is not universally appreciated nor accepted. If this key idea were not true, then this book would be dedicated to the discussion of the one most perfect circuit for all situations.

SPC circuits do exist which have been very carefully synthesized to have as many desirable and as few undesirable characteristics as possible. The Cuk SPC circuit and its variations discussed in Chapter 7 are good examples. To an amazing degree, concerted efforts such as these have succeeded in producing designs

#### 8 MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

which are near optimum for many applications. Despite these successes, however, SPC circuits such as the Ćuk versions are still not optimum for all applications.

What makes Key Idea #4 so important is the fact that even relatively small changes in SPC circuit topology often lead to significant alterations in component stresses, or changes in dynamic control-related characteristics, such that desired conversion properties might be severely compromised. On the other hand, SPC circuit topology alteration can be an effective tool for circumventing design difficulties created by the limitations and nonideal properties of components. Therefore, it is up to the designer to make the proper choice of alteration, always keeping in mind the pros and cons of his actions.

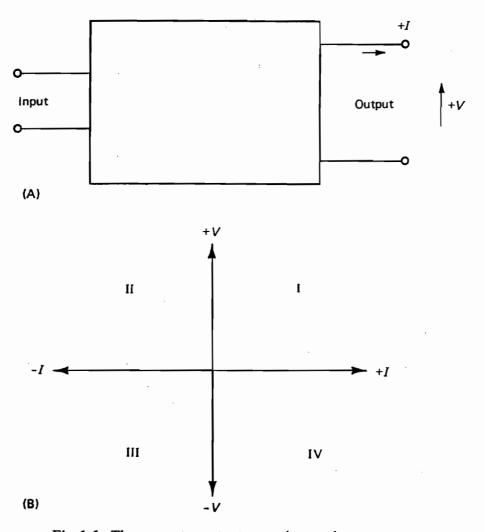

SPCs may be categorized by their general output characteristics. Sometimes, this can be most helpful to the user in defining the application requirements that must be met by an SPC. Fig. 1.6A shows a general converter system in block form, along with output voltage (V) and current (I) defined as illustrated. Fig 1.6B gives the possible directional combinations of V and I, where each quadrant

Fig. 1.6. The converter output operating quadrant concept.

is identified by sign. In a simple DC-DC converter with unidirectional power flow (input-to-output), the output is constrained to lie in either quadrant I or quadrant III of Fig. 1.6B, depending on the desired output voltage and current polarity. This is an example of single-quadrant operation. In battery charger/ discharger applications, the polarity of the converters' output potentials are fixed in sign, but their output currents may be either positive or negative in directional flow. Thus, their output characteristics must lie either in quadrants I and II or quadrants III and IV of Fig. 1.6B. This is an example of two-quadrant operation, where the power flow must be bidirectional. AC output of an SPC would also be a two-quadrant operational system. In the most general case, a converter with AC output and bidirectional power flow capability must operate in all four quadrants of Fig. 1.6B.

Before proceeding to the detailed circuit discussions of the next chapters, let us pause and review the terminology that we will be using in the text. Unfortunately, even among power electronics engineers, there is no universally accepted terminology for SPC circuit names and their operational modes, much less their origins. The present authors have taken the liberty of adopting terminology for this text which pleases us, and admittedly some of our choices are arbitrary. If the reader has adopted other conventions of terminology, he should have little difficulty in interpreting the descriptions to follow.

SPCs are often referred to as switching regulators, especially by their users. Most SPC systems do contain auxiliary control or regulating electronics to provide a constant output voltage with varying output load and input voltagehence, the appellation switching regulator. In this text, we will discuss the power stages of switching regulators and refer to them as SPCs.

The word converter is used here in its general sense, referring to a physical system that is capable of converting electrical power of one form to another form, regardless of whether its inputs and/or outputs are AC or DC in nature. This same term is sometimes used in a more restricted sense to indicate that its input and output characteristics are the same form of power, i.e., AC-AC or DC-DC. The name inverter is used when DC-AC or AC-AC power conversion is implied. Since we are restricting the discussions of this text to DC-DC SPCs, these latter distinctions will not be needed.

Alternative names exist for the buck SPC. It is not uncommon to hear this basic SPC circuit referred to as a voltage step-down converter, buck regulator, or a chopper converter. The term chopper comes from the dynamic action of the SPDT switch within the converter which produces a "chopped" voltage at the input to its low-pass filter network.

Boost converters and their basic first-order derivatives also have other names by which they are known. These names include ringing choke, flyback or voltage step-up converters. The term flyback is particularly confusing, since the same term is often applied indiscriminately by designers in discussing three very

#### 10 MODERN DC-TO-DC SWITCHMODE POWER CONVERTER CIRCUITS

different SPC circuits—the basic boost converter structure, a converter system which combines a buck and a boost converter in cascade, and a transformer-coupled version of a cascaded buck and boost converter network. In this text, the name flyback will be applied only to the last of the three alternative SPC circuits.

Buck and boost SPCs are frequently referred to as buck and boost regulators, respectively, since they are primarily used as the power stages of such regulation systems. For simplicity, we have chosen not to include these names as terms of the discussions of this text as was stated earlier in this chapter.

The adjectives buck-derived and boost-derived will be used quite frequently in the chapters to follow. When applied to a given circuit under consideration, they imply that it has been derived in some relatively direct manner from either a basic buck or a basic boost converter, respectively, and that the general properties of the parent converter have been retained. These descriptive terms will become very important as the process of evolution of large numbers of different converter topologies begins and the need to categorize them becomes evident in order to simplify the processes for application selection.

Lastly, the switching frequency  $(f_s)$  of an SPC circuit will be defined to mean the rate at which all of its circuit switches complete one full switching cycle of their operation. It is important that the switching frequency of an SPC not be confused with AC output voltage or current ripple frequencies  $(f_r)$  for, more often than not,  $f_r$  is an integer multiple of  $f_s$ . In the two basic SPC circuits to be examined in the next two chapters, their input, as well as output, ripple current frequencies are equal to the basic SPC switching frequency. However, in many other SPCs, the ripple frequencies of voltages and currents can be many times higher than the associated SPC switching frequency.

# 2. The Buck Converter

The first of the elementary switchmode power converters (SPCs) that we will examine is the buck converter. The goal of the analyses of this chapter, as well as the next one, is to develop mathematical and equivalent circuit models that adequately represent circuit operation and to quantitatively determine essential electrical characteristics required for proper design. In the analysis process, we will derive most of the expressions from which numerical values for circuit performance and component stresses may be computed.

A highly desirable feature of any electrical circuit model is that it be readily manipulated using the techniques of linear circuit analysis and synthesis familiar to electrical engineers. Unfortunately, SPC circuits are nonlinear and discontinuous by their very nature, and, as such, are very cumbersome to analyze directly using standard linear circuit theory. A major part of this chapter is therefore devoted to "linearizing" the buck converter circuit model so that it can be easily analyzed. The linearizing process does involve a slight compromise in accuracy, but for most of the quantities we are seeking, the accuracy of the model is more than adequate for normal design purposes.

The models to be derived must possess many other virtues as well. An SPC is rarely used as a power processing system unto itself. There are usually additional networks such as sequence, monitor, and control electronics along with input and output filters for EMI noise suppression. Sometimes an SPC will be used in conjunction with other converter circuits. For reasons such as these, any SPC models of practical use must be able to accommodate any additional circuit elements as easily as possible.

Another constraint placed on our SPC models is the need to recognize the nonideal character of real circuit components, such as inductor winding resistance and core loss or the equivalent series resistance (ESR) of filter capacitors, and to be able to insert these parasitic elements into the models without undue complexity in the incorporation process.

Finally, our models must be sufficiently easy to use, so that they can be applied easily by the SPC designer in his work. A model, regardless of how accurate it may be, cannot be a general purpose design tool if many hours of calculation are

required to generate the desired information. An SPC is expected to be efficient in its translation of power, and no less can be expected of its modeling abilities from a time viewpoint. The models that we will derive in this chapter and in Chapter 3 meet these requirements amazingly well.

The following modeling discussion tries to minimize the use of mathematics. As a result, some basic assumptions have been glossed over and most theoretical derivations have been omitted. For the reader who may be interested in these mathematical details, an excellent exposition of state-space averaging is given in Refs. 1 and 2 in the text bibliography of this book.

We begin by taking a very simple look in Section 2.1 at the circuit operation and waveforms for an ideal buck converter. Then, in Section 2.2, equations for the large-signal steady-state behavior for both conduction modes of this SPC will be presented. Section 2.3 will review the circuit's large-signal dynamic characterization. In Section 2.4, we will derive the small-signal characterization as well as a circuit model for the continuous mode of the buck SPC, using the state-space averaging technique. Parasitic elements will be included in this small-signal model. Finally, in Section 2.5, we will examine the operation of an ideal buck converter in a discontinuous mode situation and, once again using the methods of state-space averaging, derive the describing equations and a circuit model for this second operating mode.

The discussion of Section 2.4 is intended to demonstrate the procedure of state-space averaging. While this procedure is somewhat involved (and is really an overkill for the simple case of an ideal buck SPC), it is important to familiarize ourselves with these methods, as they are the only practical means for modeling both the discontinuous mode of a buck SPC and all modes of operation of a boost converter.

A basic assumption throughout the analysis to follow is that the output voltage ripple of the SPC is small. This is equivalent to saying that the output filter corner frequency  $(f_c)$  is much lower than the switching frequency  $(f_s)$ . This assumption is one of the key means by which a linear SPC circuit model can be formulated and is fundamental to the principles of state-space averaging. Fortunately, the assertion that  $f_s$  is much greater than  $f_c$  is valid for any SPC producing a DC output with low AC ripple content.

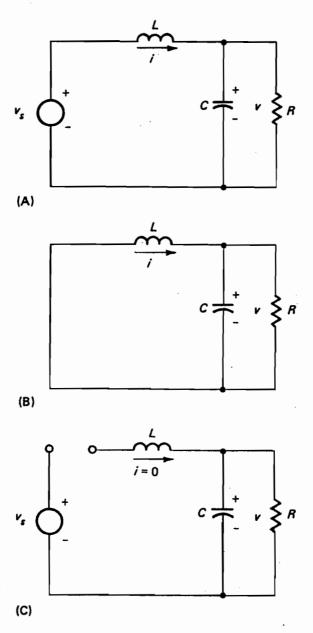

#### 2.1. BUCK CONVERTER OPERATION

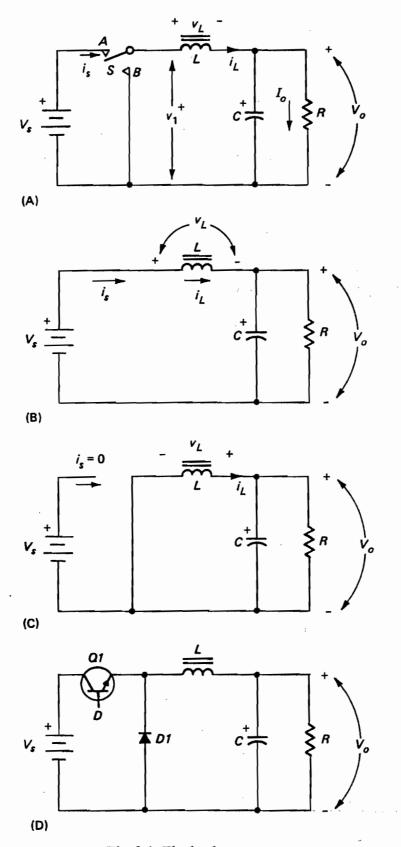

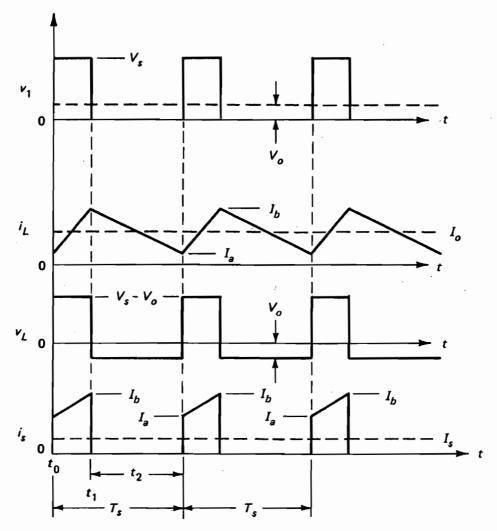

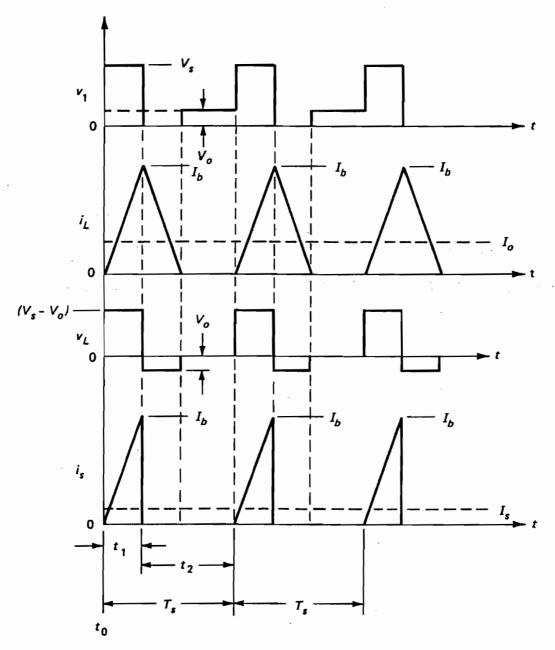

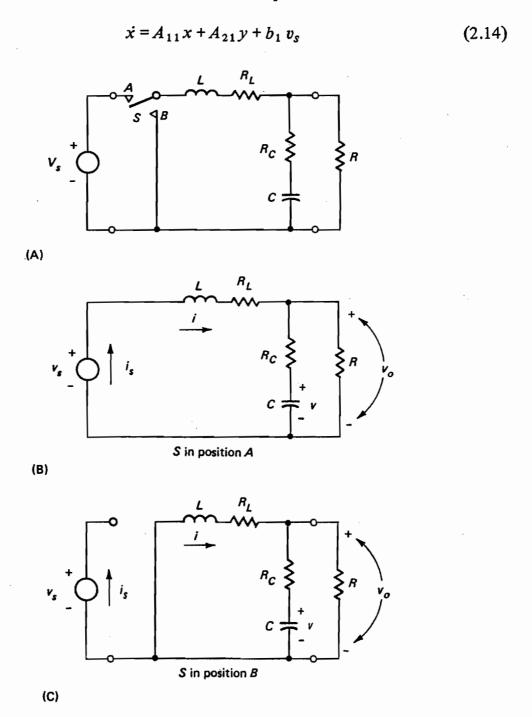

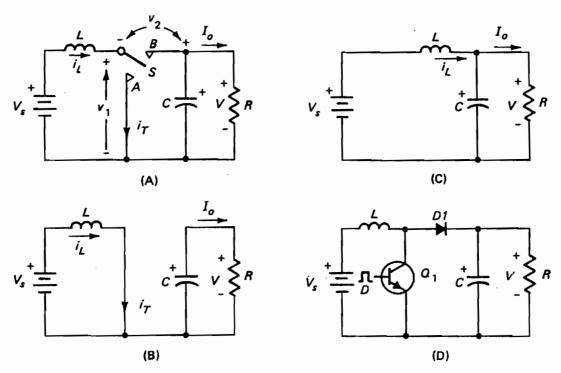

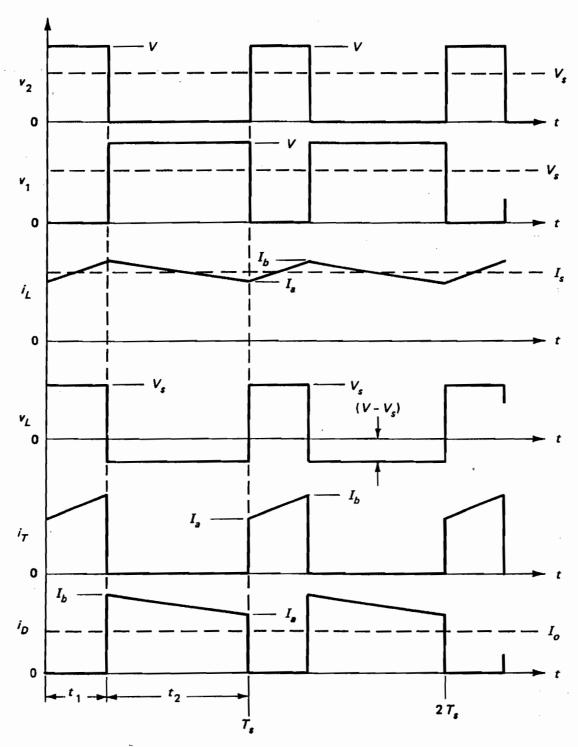

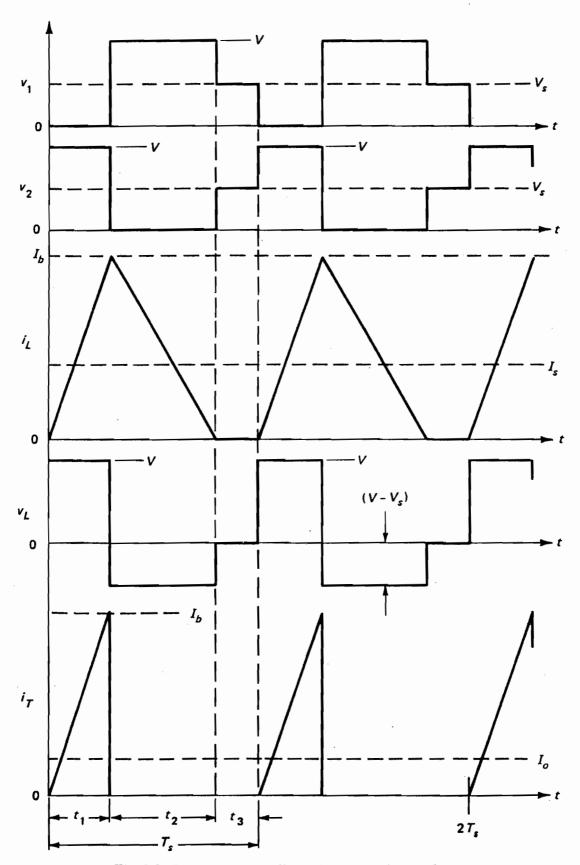

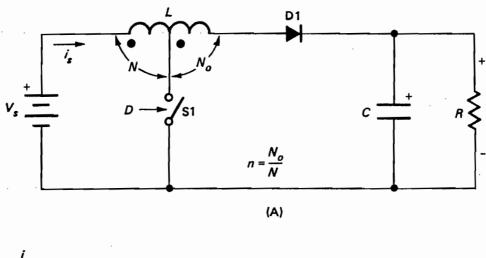

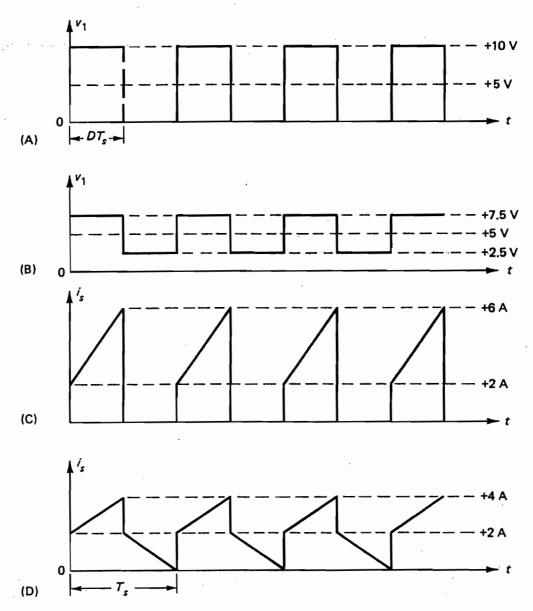

An idealized circuit for the switch states of a buck SPC is shown in Figs. 2.1B and 2.1C, along with a practical realization for the SPDT switch in Fig. 2.1D. Corresponding typical waveforms for the ideal buck converter of Fig. 2.1A are diagrammed in Figs. 2.2 and 2.3.

During the switching cycle, the SPDT switch (S) moves between positions A and B, so that the circuit topology alternates states between that of Fig. 2.1B and that of 2.1C. At the beginning of a switching cycle  $(t_0)$ , S is in position A, the

Fig. 2.1 The buck converter.

Fig. 2.2. Buck converter waveforms for the continuous mode of operation.

input voltage  $(V_s)$  is greater than the output voltage  $(V_o)$ , and the current  $(i_L)$  in the inductor (L) ramps upward during the interval  $t_1$ , as shown in Fig. 2.2.

The inductor current will continue to ramp upward until S changes to position B. When S moves to position B, at  $t = t_1$ ,  $V_S = 0$  and the voltage across L changes sign with  $i_L$  ramping downward. Two inductor current possibilities now exist at the end of interval  $t_2$ ; either  $i_L = 0$  or  $i_L = I_a$ , some nonzero positive value. In other words, either all of the energy stored in L is delivered to the load between  $t_1$  and  $t_2$  or some energy remains as S moves back to position A.

This defines the two basic operating conditions for the buck SPC and leads to a key idea about SPC operating modes:

MODE 1. Continuous inductor current during the entire switching cycle (continuous mode operation).

MODE 2. Discontinuous inductor current during the switching cycle (discontinuous mode operation).

Fig. 2.3. Buck converter waveforms for the discontinuous mode of operation.

#### Key Idea #5

THE CONDUCTION MODE OF THE INDUCTOR CURRENT IS A FUNDAMENTAL FACTOR IN DETERMINING THE ELECTRICAL CHARACTERISTICS OF ANY SPC.

If one were to place two topologically identical SPCs in separate black boxes, the only difference between them being that the value of the inductor of one is chosen so the converter operates in the continuous mode and the other inductor chosen such that its SPC operates in the discontinuous mode, a series of

tests on each SPC to determine output electrical characteristics would conclude that the two boxes contained entirely different converter circuits. The inductor current conduction modes of the basic SPCs (as well as any complex derivatives) have a profound effect on their conversion characteristics and are as important to know as their topological structures when determining circuit performance.

The duty cycle (D) is defined as:

$$D \equiv \frac{t_1}{T_s} = t_1 f_s . \tag{2.1}$$

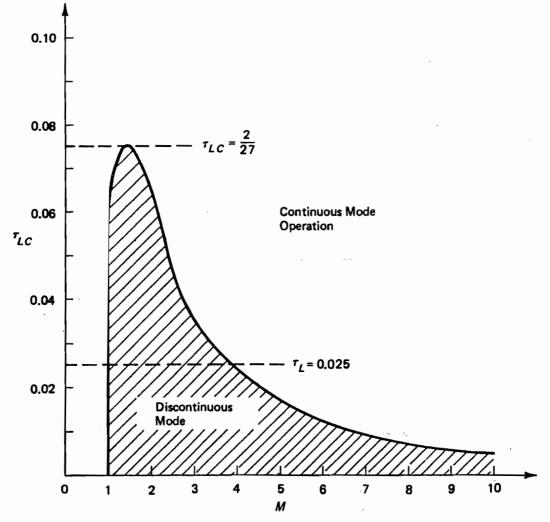

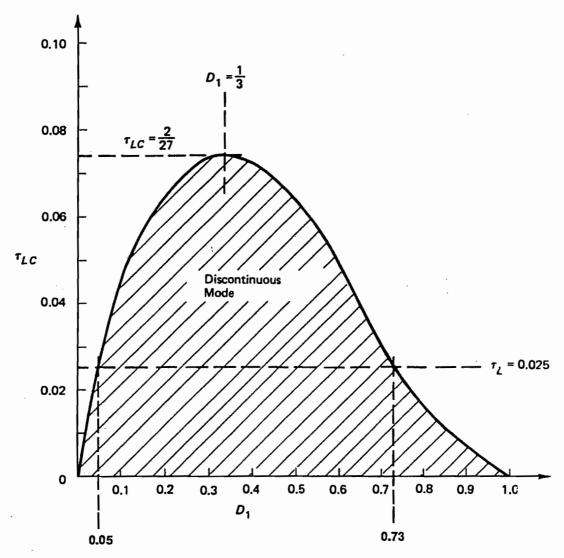

For fixed values of L and D, the mode in which the buck converter operates is determined by the value of R. As R is increased in ohmic value, the operating mode will change from continuous to discontinuous. On the other hand, if R and D are fixed, the operating mode will change from continuous to discontinuous as the inductance of L is decreased. As  $f_s$  is increased, the minimum value of L to maintain the SPC in a continuous mode of operation will decrease in direct proportion to the change in  $f_s$ .

As this discussion proceeds, it will become apparent that, for many applications such as those where high-power or multiple outputs from an SPC are required, maintaining the SPC in a continuous mode of operation is very desirable, even for large variations in load resistances. To avoid using an excessively large value of L to maintain continuous current levels at light output loads, a "swinging" choke is sometimes employed. A swinging choke is an inductance whose value is a function of the current passing through it, being large at low current and getting progressively smaller as the current is increased. While this technique can be very useful, a swinging inductance will complicate the analysis of the SPC by making  $f_c$  of its associated filter variable with load resistance. This may make the stabilization of any associated regulatory control loop somewhat more difficult.

One can deduce many of the properties characteristic of a buck SPC and its more complex derivatives by examining its electrical waveforms, such as those plotted in Figs. 2.2 and 2.3.

$V_o$  is the average voltage value of  $v_1$  so this converter can be simply viewed as a voltage chopper followed by a low-pass filter. Voltage  $v_1$  is composed of both AC and DC components. Since its DC voltage component is the desired output of the converter, the low-pass filter must remove any AC component of this time-varying potential. This implies that  $f_c$  of the output low-pass filter must be much less than  $f_s$ . Because  $V_o$  is the average of  $v_1$ ,  $V_o$  must always be less than the input DC voltage  $(V_s)$  to this SPC.

Notice also that the waveform for  $v_1$  differs in shape for each of the two modes of operation. In the continuous mode,  $v_1 = V_s$  during  $t_1$ , and  $v_1 = 0$  during the entire period  $t_2$ . The average value of  $v_1(V_o)$  is determined by D only

and, ideally,  $V_o$  would be independent of R in this mode. In the discontinuous mode, however,  $v_1$  can be either zero or equal to  $V_o$  during time  $t_2$ . The length of time spent by  $v_1$  in a zero-value condition during  $t_2$  is determined by R. The value of  $V_o$  is now dependent on R as well as D. A close examination of the  $v_1$  waveforms in Figs. 2.2 and 2.3 shows that, for the same value of  $V_s$  and D,  $V_o$  was increased in the discontinuous mode. Figs, 2.2 and 2.3 have been scaled so that both SPC output power levels are the same in value.

The input current  $(i_s)$  is always pulsating, regardless of the operating mode of the buck SPC. Most applications limit (often severely) the amount of pulsating current that can be drawn by an SPC from its source of power. In normal practice, some form of a low-pass filter network is inserted between the source of power and the input terminals of the SPC. As will be shown in Chapter 10, the presence of such a filter must be accounted for at an early stage of SPC design and modeling process. Failure to do so can result in a very unpleasant surprise in the form of self-oscillations when the SPC and the input low-pass filter circuit are united.

The average value of  $i_s$  is determined both by  $V_o$  and R. In an ideal buck converter with no power losses, efficiency  $(\eta)$  of power conversion is 100%. Therefore,

$$V_s I_s = \frac{V_o^2}{R}, \quad \eta = 100\%.$$

(2.2)

For the normal case with a constant value of  $V_o$ ,  $V_o^2 = K$ . In this instance,

$$I_{s} = \frac{K}{V_{s}R}. (2.3)$$

Here, the average input current value is inversely proportional to both  $V_s$  and R. However, the pulsating value for  $i_s$  is determined by  $i_L$  which, in turn, is a function of R, but not  $V_s$ . As  $V_s$  is varied and D altered to maintain a constant  $V_o$ , the width of  $i_s$  is altered, but not its maximum amplitude  $I_b$ .

The current  $i_s$  is the input switch current, and it can be seen from Figs. 2.2 and 2.3 that, for a constant value of input power, the peak magnitude of  $i_s$  is much higher when the buck SPC is operating in a discontinuous mode of operation. In a practical realization of the SPDT switch as shown in Fig. 2.1D, both the BJT (S1) and the diode (D1) must possess a much higher peak-power handling capability if SPC operation in the discontinuous mode is desired. For this and many other important reasons, continuous mode of operation of buck SPCs is normally preferred in high-power applications, even though their inductances must be larger and therefore, heavier and certainly more expensive.

The output filter cutoff frequency is defined as

$$f_c = \frac{1}{2\pi\sqrt{LC}} \tag{2.4}$$

and it would appear that L can be chosen to be just large enough to maintain the SPC in a continuous mode, with C then selected to provide the degree of output filtering desired. Unfortunately, capacitors are not perfect electrical elements and some power will be dissipated in their ESR. The ESR voltage drop produces an output ripple voltage that can only be reduced by lowering ESR magnitude or the dynamic capacitor current causing the ripple. The size of C is more often determined by the ripple current magnitude than by the value desired for  $f_c$ . Making L larger reduces the output ripple current value which, in turn, reduces C. In actual design practice, there is usually a tradeoff made in selecting L and C for weight and size plus cost reasons. In high-power converters, such tradeoffs normally result in a value selection for L which places the SPC circuit operating well into the continuous mode at full load.

Ideally, the output current  $(I_o)$  of the buck SPC is not a pulsating quantity since the ripple content of  $i_L$  is small in the continuous mode. This is a convenient feature for many applications and, frequently, additional output filtering can be either dispensed with or made quite small.

#### 2.2 STEADY-STATE LARGE-SIGNAL CHARACTERIZATION

To design a converter, it is necessary to quantify many of the circuit characteristics, such as the AC and DC currents flowing through its circuit elements, the voltages across these elements, the input-to-output voltage transfer ratio as a function of D, and many other factors.

The following discussion presents equations and graphs that describe the large-signal steady-state (DC) characteristics of a buck SPC. The analysis presumes an ideal buck SPC, i.e., no parasitic elements such as inductor series resistance  $(R_L)$  or capacitor ESR  $(R_c)$  are included. Despite this limitation, the equations presented still have more than adequate accuracy for practical design purposes. For an SPC to be efficient,  $R_L$  and  $R_c$  must be made small. Designers often go to great lengths to minimize lossy parasitic elements when engineering SPC circuits. Therefore, their omission from the following model derivation is justified as a matter of good design practice.

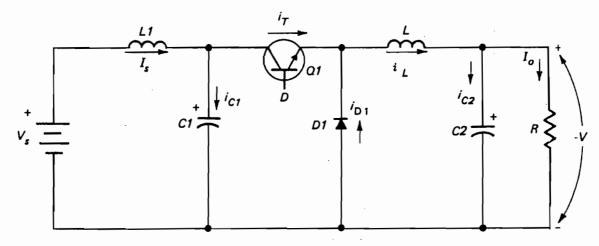

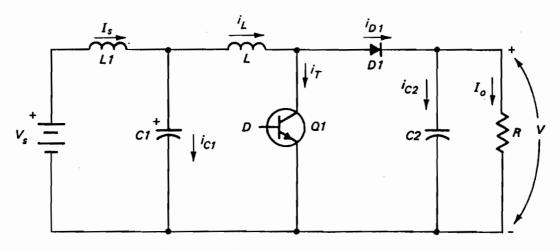

Figure 2.4 illustrates the buck SPC for which the equations in Tables 2.1 and 2.2 apply. An input filter network has been included (L1, C1), and it is presumed that L1 possesses sufficient inductance so that  $I_s$  is essentially DC. On the output side, C2 is assumed to be high in capacitance, so that the AC component of  $I_L$  flows only through this filter element. Both of these assumptions are consistent with practical application requirements of SPCs for both low input current ripple and small output voltage ripple.

Fig. 2.4. Definition of the buck converter component currents....

For the equations shown in Tables 2.1 and 2.2, and later in Table 2.3, the following definitions apply:

$$D \equiv D_1 = \frac{t_1}{T_s} \quad \text{(switch conduction duty cycle)} \tag{2.5}$$

$$M = \frac{V}{V_c}$$

(input-to-output DC transfer ratio) (2.6)

$$\tau_L \equiv \frac{L}{RT_s}$$

(normalized inductor time constant) (2.7)

$$I_o = \frac{V}{R}$$

(DC output current) (2.8)

TABLE 2.1A. Definitions of Variables for the Buck Converter Equations.

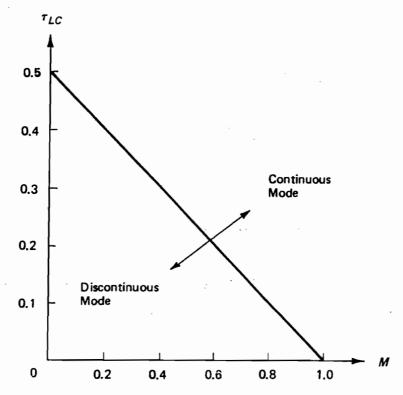

| $	au_L$           | $L/RT_s$                    |

|-------------------|-----------------------------|

| $T_{\mathcal{S}}$ | Switching period            |

| $	au_{LC}$        | $L_c/RT_s$                  |

| $L_c$             | Critical inductance         |

| $\tau_{LC}$       | (1-M)/2                     |

| $D_1$             | Switch ON duty cycle        |

| $D_2$             | Diode conduction duty cycle |

| M                 | $V/V_{\rm s}$               |

| $I_a$             | Minimum inductor current    |

| $I_h$             | Maximum inductor current    |

TABLE 2.1B. Buck Converter Equations for Continuous Inductor Current.

| Denoudent                  |                                                                                                                    |                                                                                                                          |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Dependent<br>Variable      | $f(M, \tau_L, V, R)$                                                                                               | $f(D_1, \tau_L, V, R)$                                                                                                   |  |  |

| M                          | М                                                                                                                  | $D_1$                                                                                                                    |  |  |

| $D_1$                      | <i>M</i>                                                                                                           | $\dot{\mathcal{D}}_1$                                                                                                    |  |  |

| $D_2$                      | 1 - M                                                                                                              | 1 - D <sub>1</sub>                                                                                                       |  |  |

| $I_a (I_{L(\min)})$        | $\frac{V}{R} \left[ 1 - \left( \frac{1 - M}{2\tau_L} \right) \right]$                                              | $\frac{V}{R} \left[ 1 - \left( \frac{1 - D_1}{2\tau_L} \right) \right]$                                                  |  |  |

| $I_b (I_{L \text{(max)}})$ | $\frac{V}{R}\left[1+\left(\frac{1-M}{2\tau_L}\right)\right]$                                                       | $\frac{V}{R}\left[1+\left(\frac{1-D_1}{2\tau_L}\right)\right]$                                                           |  |  |

| $I_{L(\mathrm{avg})}$      | $\frac{V}{R}$                                                                                                      | $\frac{v}{R}$                                                                                                            |  |  |

| $I_{L(\rm rms)}$           | $\frac{V}{R} \left[ 1 + \frac{1}{12} \left( \frac{1 - M}{\tau_L} \right)^2 \right]^{1/2}$                          | $\frac{V}{R} \left[ 1 + \frac{1}{12} \left( \frac{1 - D_1}{\tau_{L}} \right)^2 \right]^{1/2}$                            |  |  |

| I <sub>C1(rms)</sub>       | $\frac{V}{R}\left\{M\left[(1-M)+\frac{1}{12}\left(\frac{1-M}{\tau_L}\right)^2\right]\right\}^{1/2}$                | $\frac{V}{R} \left\{ D_1 \left[ (1 - D_1) + \frac{1}{12} \left( \frac{1 - D_1}{\tau_L} \right)^2 \right] \right\}^{1/2}$ |  |  |

| I <sub>C2(rms)</sub>       | $\frac{V}{R} \left( \frac{1 - M}{\sqrt{12}\tau_L} \right)$                                                         | $\frac{V}{R} \left( \frac{1 - D_1}{\sqrt{12} \tau_L} \right)$                                                            |  |  |

| $I_{T(avg)}$               | $\frac{VM}{R}$                                                                                                     | $\frac{VD_1}{R}$                                                                                                         |  |  |

| $I_{T(rms)}$               | $\frac{V}{R} \left\{ M \left[ 1 + \frac{1}{12} \left( \frac{1 - M}{\tau_L} \right)^2 \right] \right\}^{1/2}$       | $\frac{V}{R} \left\{ D_1 \left[ 1 + \frac{1}{12} \left( \frac{1 - D_1}{\tau_L} \right)^2 \right] \right\}^{1/2}$         |  |  |

| I <sub>D1(avg)</sub>       | $\frac{V}{R}(1-M)$                                                                                                 | $\frac{V}{R}(1-D_1)$                                                                                                     |  |  |

| I <sub>D1(rms)</sub>       | $\frac{V}{R} \left\{ (1 - M) \left[ 1 + \frac{1}{12} \left( \frac{1 - M}{\tau_L} \right)^2 \right] \right\}^{1/2}$ | $\frac{V}{R} \left\{ (1 - D_1) \left[ 1 + \frac{1}{12} \left( \frac{1 - D_1}{\tau_L} \right)^2 \right] \right\}^{1/2}$   |  |  |

| I <sub>s(avg)</sub>        | \frac{VM_{\circ}}{R}                                                                                               | $\frac{VD_1}{R}$                                                                                                         |  |  |

$$D_2 \equiv \frac{t_2}{T_s}$$

(diode conduction duty cycle). (2.9)

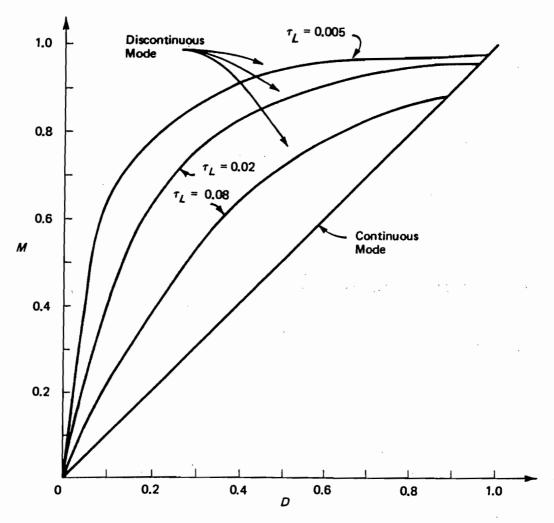

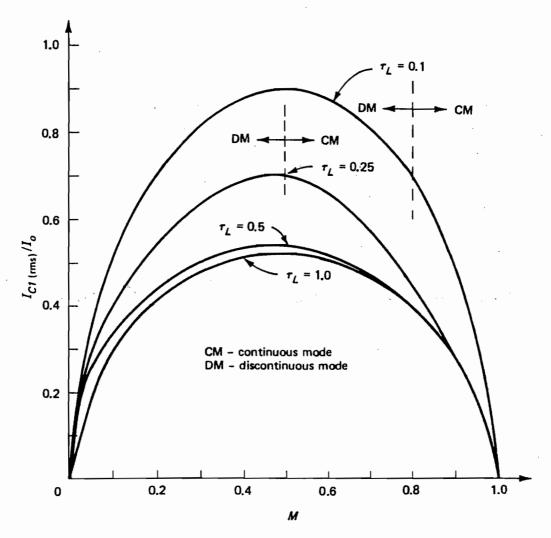

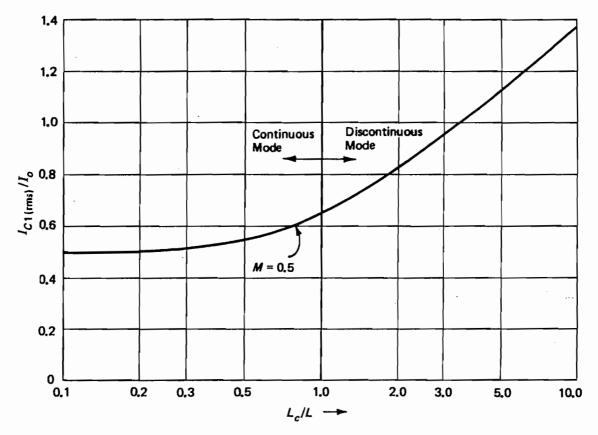

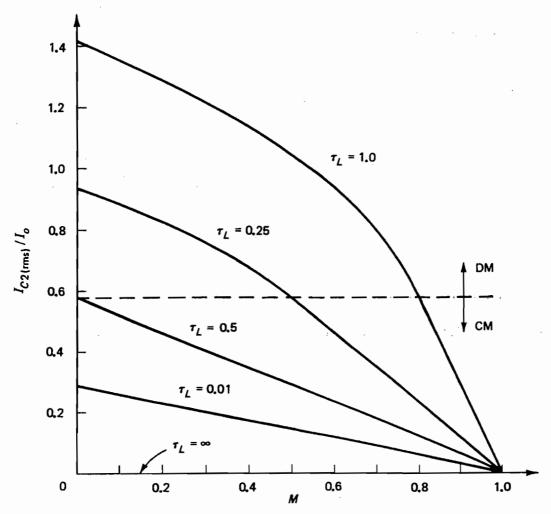

The equations in these tables have been stated in two different ways—first as a function of  $D_1$  for closed-loop calculations, and second as a function of M for open-loop operation. For the continuous mode,  $D_1 = M$ , so that the two columns

TABLE 2.2A. Buck Converter Equations for Discontinuous Inductor Current.

| Dependent<br>Variable |                                                                                                 |                                                                                                                                                      |  |

|-----------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| М                     | М                                                                                               | $\frac{2}{1 + \sqrt{1 + 8\tau_L/D_1^2}}$                                                                                                             |  |

| <i>D</i> <sub>1</sub> | $M \sqrt{\frac{2\tau_L}{1-M}}$                                                                  | $D_1$                                                                                                                                                |  |

| D <sub>2</sub>        | $\sqrt{2\tau_L (1-M)}$                                                                          | $\left(\frac{4\tau_L}{D_1}\right)\left(\frac{1}{1+\sqrt{1+8\tau_L/D_1^2}}\right)$                                                                    |  |

| $I_a$                 | .0                                                                                              | 0                                                                                                                                                    |  |

| $I_b$                 | $\frac{V}{R}\sqrt{\frac{2(1-M)}{\tau_L}}$                                                       | $\left(\frac{\nu}{R}\right)\left(\frac{4}{D_1}\right)\left(\frac{1}{1+\sqrt{1+8\tau_L/D_1^2}}\right)$                                                |  |

| $I_{L(avg)}$          | $\frac{V}{R}$                                                                                   | $\frac{V}{R}$                                                                                                                                        |  |

| $I_{L(rms)}$          | $\frac{V}{R} \left[ \left( \frac{8}{9} \right) \left( \frac{1-M}{\tau_L} \right) \right]^{1/4}$ | $I_{b}\left[\frac{D_{1}+D_{2}}{3}\right]^{1/2}$                                                                                                      |  |

| I <sub>C1(rms)</sub>  | $\frac{V}{R} \left[ M \sqrt{\frac{8}{9} \left( \frac{1-M}{\tau_L} \right)} - M^2 \right]^{1/2}$ | $I_{b}\sqrt{\frac{D_{1}}{3}-\frac{D_{1}^{2}}{4}}$                                                                                                    |  |

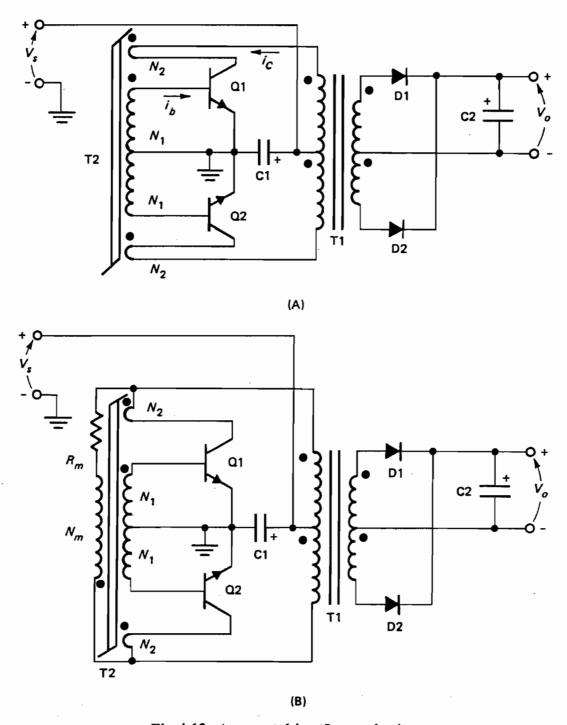

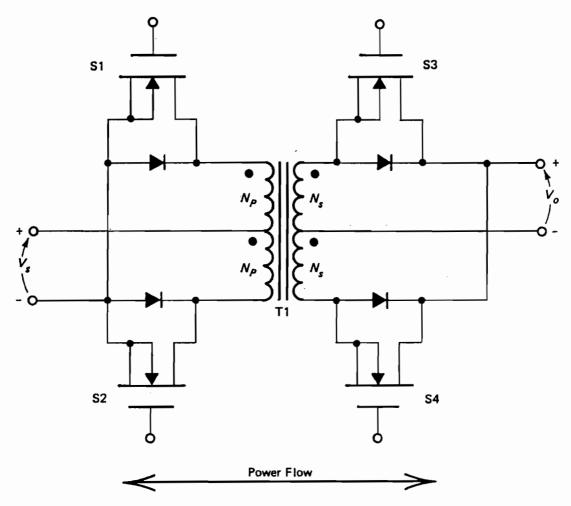

| I <sub>C2(rms)</sub>  | $\frac{V}{R} \left[ \sqrt{\frac{8}{9} \left( \frac{1-M}{\tau_L} \right)} - 1 \right]^{1/2}$     | $I_b \left[ \frac{D_1 + D_2}{3} - \frac{(D_1 + D_2)^2}{4} \right]^{1/2}$                                                                             |  |